၄ လက်မ SiC ဝေဖာ 6H တစ်ဝက်လျှပ်ကာ SiC အောက်ခံများ prime၊ research နှင့် dummy grade

ထုတ်ကုန် သတ်မှတ်ချက်

| အဆင့် | သုည MPD ထုတ်လုပ်မှုအဆင့် (Z အဆင့်) | စံထုတ်လုပ်မှုအဆင့် (P အဆင့်) | အတုအယောင်အဆင့် (D အဆင့်) | ||||||||

| အချင်း | ၉၉.၅ မီလီမီတာ ~ ၁၀၀.၀ မီလီမီတာ | ||||||||||

| 4H-SI | ၅၀၀ မိုက်ခရိုမီတာ ± ၂၀ မိုက်ခရိုမီတာ | ၅၀၀ မိုက်ခရိုမီတာ ± ၂၅ မိုက်ခရိုမီတာ | |||||||||

| ဝေဖာ ဦးတည်ချက် |

ဝင်ရိုးပြင်ပ: 4H-N အတွက် <1120 > ±0.5° ဘက်သို့ 4.0°၊ ဝင်ရိုးပေါ်တွင်: 4H-SI အတွက် <0001>±0.5° | ||||||||||

| 4H-SI | ≤၁ စင်တီမီတာ-2 | ≤၅ စင်တီမီတာ-2 | ≤၁၅ စင်တီမီတာ-2 | ||||||||

| 4H-SI | ≥1E9 Ω·စင်တီမီတာ | ≥1E5 Ω·စင်တီမီတာ | |||||||||

| အဓိက ပြားချပ်ချပ် အနေအထား | {၁၀-၁၀} ±၅.၀° | ||||||||||

| အဓိကပြားချပ်အရှည် | ၃၂.၅ မီလီမီတာ ± ၂.၀ မီလီမီတာ | ||||||||||

| ဒုတိယပြားချပ်အရှည် | ၁၈.၀ မီလီမီတာ ± ၂.၀ မီလီမီတာ | ||||||||||

| ဒုတိယပြားချပ်ချပ် ಒಟ್ಟಾರೆ | ဆီလီကွန်ကို အပေါ်ဘက်သို့ မျက်နှာမူထားသည်- 90° CW။ Prime flat မှ ±5.0° | ||||||||||

| အနားသတ်ဖယ်ထုတ်ခြင်း | ၃ မီလီမီတာ | ||||||||||

| LTV/TTV/Bow /Warp | ≤3 μm/≤5 μm/≤15 μm/≤30 μm | ≤10 μm/≤15 μm/≤25 μm/≤40 μm | |||||||||

| ကြမ်းတမ်းမှု | မျက်နှာ C | ပိုလန် | Ra≤1 nm | ||||||||

| စီ မျက်နှာ | စီအမ်ပီ | Ra≤0.2 nm | Ra≤0.5 nm | ||||||||

| မြင့်မားသော အလင်းကြောင့် အနားစွန်း အက်ကွဲကြောင်းများ | မရှိပါ | စုစုပေါင်းအရှည် ≤ ၁၀ မီလီမီတာ၊ တစ်ခုတည်း အရှည် ≤၂ မီလီမီတာ | |||||||||

| မြင့်မားသောပြင်းထန်မှုအလင်းဖြင့် Hex ပြားများ | စုစုပေါင်းဧရိယာ ≤0.05% | စုစုပေါင်းဧရိယာ ≤0.1% | |||||||||

| မြင့်မားသော ပြင်းထန်မှုရှိသော အလင်းရောင်ဖြင့် Polytype ဧရိယာများ | မရှိပါ | စုစုပေါင်းဧရိယာ ≤3% | |||||||||

| မြင်သာသော ကာဗွန် ပါဝင်မှုများ | စုစုပေါင်းဧရိယာ ≤0.05% | စုစုပေါင်းဧရိယာ ≤3% | |||||||||

| မြင့်မားသော အလင်းကြောင့် ဆီလီကွန် မျက်နှာပြင် ခြစ်ရာများ | မရှိပါ | စုစုပေါင်းအရှည် ≤1 *ဝေဖာအချင်း | |||||||||

| အလင်းအမှောင်ကြောင့် မြင့်မားသော Edge Chips များ | အကျယ်နှင့်အနက် ≥၀.၂ မီလီမီတာ ခွင့်မပြုပါ။ | ၅ ခု ခွင့်ပြုထားသည်၊ တစ်ခုလျှင် ၁ မီလီမီတာ ≤ | |||||||||

| မြင့်မားသောပြင်းထန်မှုကြောင့် ဆီလီကွန်မျက်နှာပြင်ညစ်ညမ်းမှု | မရှိပါ | ||||||||||

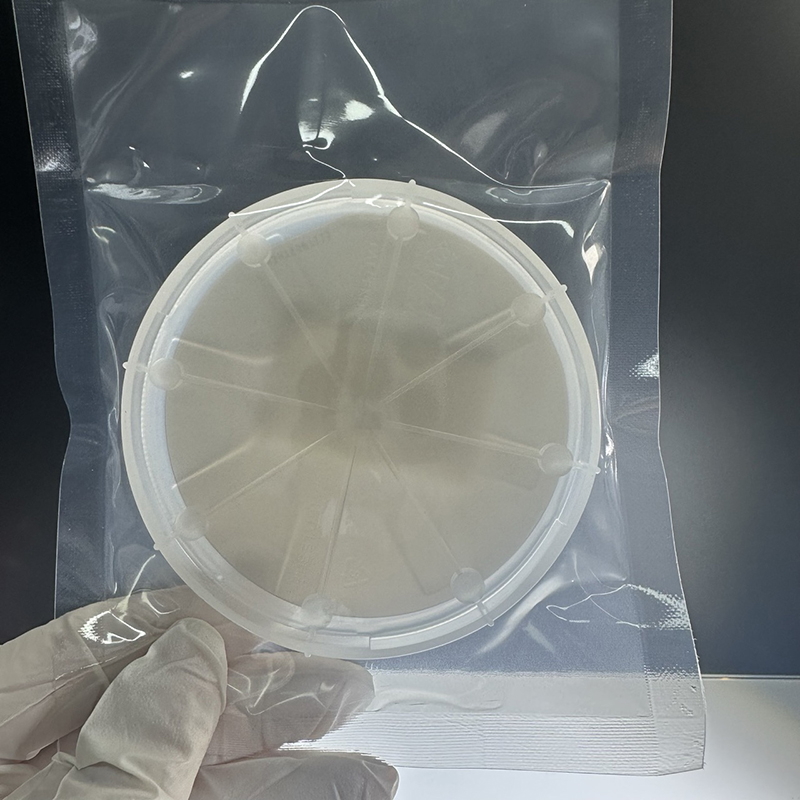

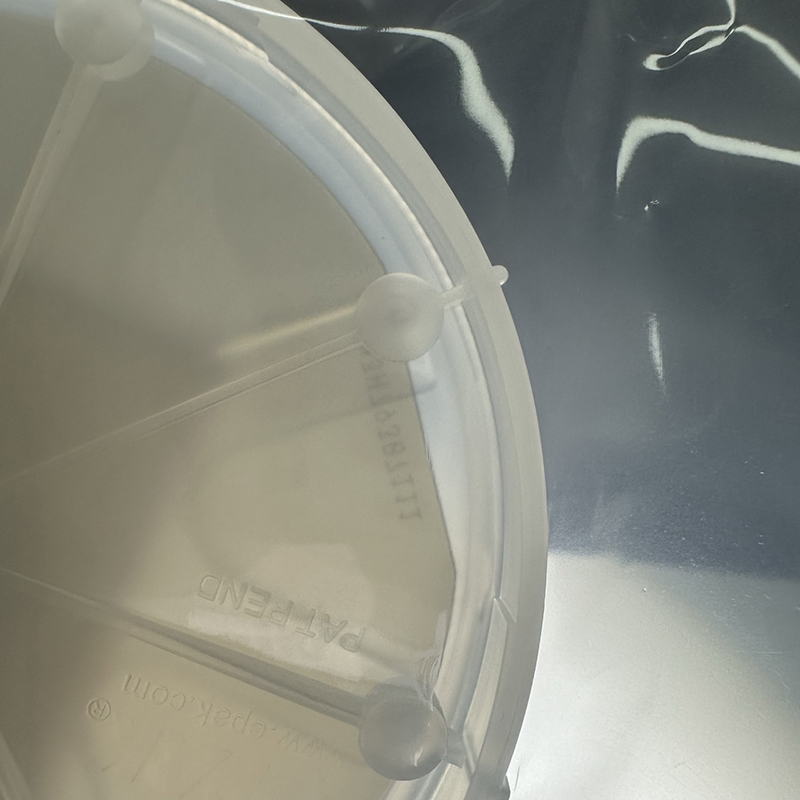

| ထုပ်ပိုးခြင်း | ဝဖာများစွာပါဝင်သော ကက်ဆက် သို့မဟုတ် ဝဖာကွန်တိန်နာတစ်ခုတည်း | ||||||||||

အသေးစိတ်ပုံကြမ်း

ဆက်စပ်ထုတ်ကုန်များ

သင့်စာကို ဤနေရာတွင် ရေးပြီး ကျွန်ုပ်တို့ထံ ပေးပို့ပါ။