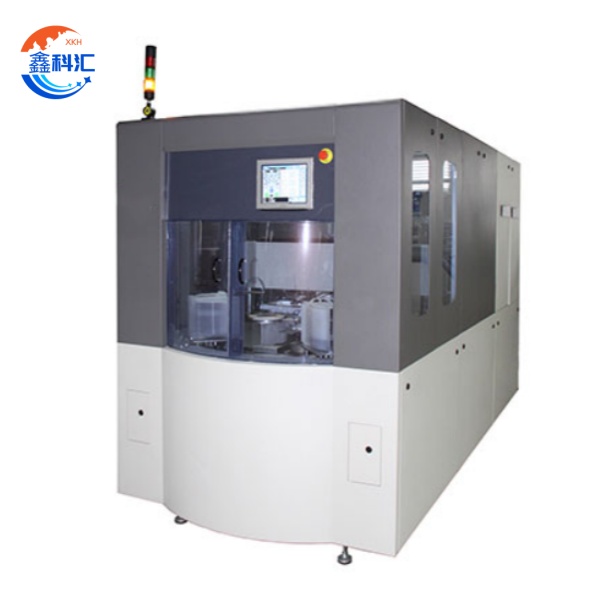

၄ လက်မမှ ၁၂ လက်မအထိ Sapphire/SiC/Si ဝေဖာများ ပြုလုပ်ရန်အတွက် ဝေဖာပါးလွှာစေသည့် စက်ပစ္စည်း

အလုပ်လုပ်ပုံ အခြေခံမူ

wafer thinning လုပ်ငန်းစဉ်သည် အဆင့်သုံးဆင့်ဖြင့် လုပ်ဆောင်သည်-

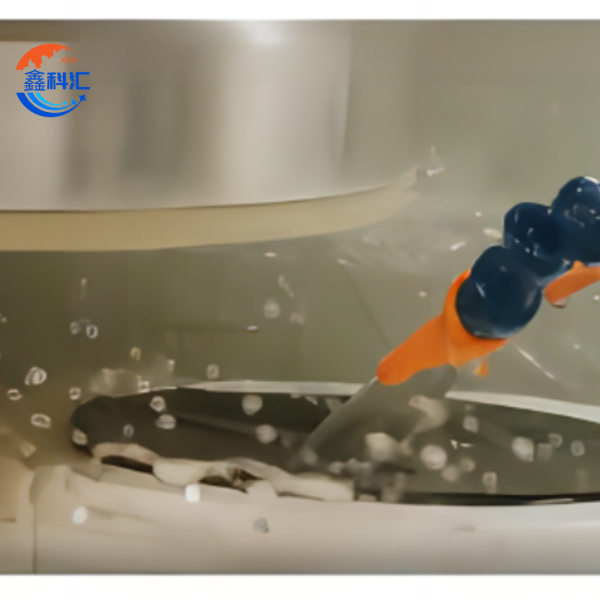

ကြမ်းတမ်းစွာ ကြိတ်ခွဲခြင်း- စိန်ဘီး (ဂရစ်အရွယ်အစား 200–500 μm) သည် ပစ္စည်း 50–150 μm ကို 3000–5000 rpm တွင် ဖယ်ရှားပေးခြင်းဖြင့် အထူကို လျင်မြန်စွာ လျှော့ချပေးပါသည်။

အနုစိတ်ကြိတ်ခွဲခြင်း- ပိုမိုအနုစိတ်သောဘီး (ဂရစ်အရွယ်အစား 1–50 μm) သည် <1 μm/s တွင် အထူကို 20–50 μm အထိ လျှော့ချပေးပြီး မြေအောက်ပျက်စီးမှုကို အနည်းဆုံးဖြစ်စေသည်။

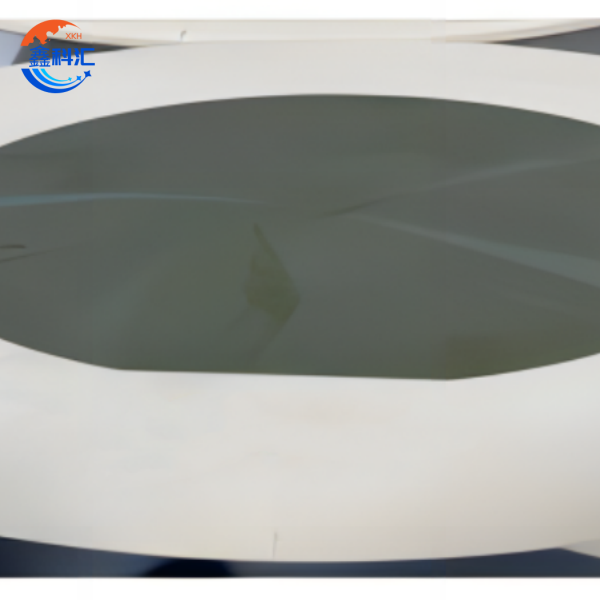

ඔප දැමීම (CMP): ဓာတု-စက်ပိုင်းဆိုင်ရာ အရည်သည် ကျန်ရှိနေသော ပျက်စီးမှုများကို ဖယ်ရှားပေးပြီး Ra <0.1 nm ကို ရရှိစေပါသည်။

လိုက်ဖက်သောပစ္စည်းများ

ဆီလီကွန် (Si): CMOS ဝေဖာများအတွက် စံ၊ 3D stacking အတွက် 25 μm အထိ ပါးလွှာအောင် ပြုလုပ်ထားသည်။

ဆီလီကွန်ကာဗိုက် (SiC): အပူတည်ငြိမ်မှုအတွက် အထူးပြုလုပ်ထားသော စိန်ဘီးများ (စိန်ပါဝင်မှု ၈၀%) လိုအပ်သည်။

နီလာ (Al₂O₃): UV LED အသုံးချမှုများအတွက် 50 μm အထိ ပါးလွှာအောင် ပြုလုပ်ထားသည်။

အဓိကစနစ် အစိတ်အပိုင်းများ

၁။ ကြိတ်ခွဲစနစ်

နှစ်ထပ်ဝင်ရိုးကြိတ်စက်- ကြမ်းတမ်း/အနုစိတ်ကြိတ်ခွဲခြင်းကို တစ်ခုတည်းသောပလက်ဖောင်းတွင် ပေါင်းစပ်ထားပြီး လည်ပတ်ချိန်ကို ၄၀% လျှော့ချပေးသည်။

Aerostatic Spindle: 0–6000 rpm အမြန်နှုန်းအပိုင်းအခြားဖြင့် <0.5 μm radial runout။

၂။ ဝေဖာကိုင်တွယ်စနစ်

ဖုန်စုပ်ချက်: >50 N ကိုင်ထားအားရှိပြီး ±0.1 μm နေရာချထားမှုတိကျမှုရှိသည်။

ရိုဘော့တစ်လက်မ- ၄-၁၂ လက်မ ဝေဖာများကို ၁၀၀ မီလီမီတာ/စက္ကန့်ဖြင့် သယ်ယူပို့ဆောင်သည်။

၃။ ထိန်းချုပ်ရေးစနစ်

လေဆာ အပြန်အလှန် တိုင်းတာခြင်း- အချိန်နှင့်တပြေးညီ အထူစောင့်ကြည့်ခြင်း (resolution 0.01 μm)။

AI-Driven Feedforward: ဘီးပွန်းစားမှုကို ခန့်မှန်းပြီး parameters များကို အလိုအလျောက် ချိန်ညှိပေးသည်။

၄။ အအေးခံခြင်းနှင့် သန့်ရှင်းရေး

အာထရာဆောင်း သန့်ရှင်းရေး- ၉၉.၉% ထိရောက်မှုဖြင့် ၀.၅ မိုက်ခရိုမီတာထက် ကျော်လွန်သော အမှုန်အမွှားများကို ဖယ်ရှားပေးသည်။

အိုင်းယွန်းဓာတ်ဖယ်ထုတ်ထားသောရေ- ဝေဖာကို ပတ်ဝန်းကျင်ထက် <5°C အထိ အအေးခံသည်။

အဓိကအားသာချက်များ

၁။ အလွန်မြင့်မားသော တိကျမှု- TTV (စုစုပေါင်းအထူပြောင်းလဲမှု) <0.5 μm၊ WTW (Within-Wafer အထူပြောင်းလဲမှု) <1 μm။

၂။ ဘက်စုံလုပ်ငန်းစဉ်ပေါင်းစပ်ခြင်း- စက်တစ်ခုတည်းတွင် ကြိတ်ခွဲခြင်း၊ CMP နှင့် ပလာစမာထွင်းထုခြင်းတို့ကို ပေါင်းစပ်ထားသည်။

၃။ ပစ္စည်းလိုက်ဖက်ညီမှု-

ဆီလီကွန်: အထူလျှော့ချမှုကို 775 μm မှ 25 μm အထိ။

SiC: RF အပလီကေးရှင်းများအတွက် <2 μm TTV ကို ရရှိသည်။

အရောအနှောပါဝင်သော ဝေဖာများ- ခုခံမှုရွေ့လျားမှု ၅% အောက်ရှိသော ဖော့စဖရပ်စ်အရောအနှောပါဝင်သော InP ဝေဖာများ။

၄။ စမတ်ကျသော အလိုအလျောက်စနစ်- MES ပေါင်းစပ်မှုသည် လူ့အမှားကို ၇၀% လျှော့ချပေးသည်။

၅။ စွမ်းအင်ထိရောက်မှု- ပြန်လည်အားဖြည့်ဘရိတ်အုပ်ခြင်းဖြင့် ပါဝါသုံးစွဲမှု ၃၀% လျော့နည်းသည်။

အဓိကအသုံးချမှုများ

၁။ အဆင့်မြင့်ထုပ်ပိုးမှု

• 3D ICs: Wafer thinning သည် logic/memory chips (ဥပမာ HBM stacks) များကို vertical stacking လုပ်နိုင်ပြီး 2.5D solutions များနှင့် နှိုင်းယှဉ်ပါက bandwidth 10x ပိုများပြီး power consumption 50% လျော့နည်းစေသည်။ ဤပစ္စည်းသည် hybrid bonding နှင့် <10 μm interconnect pitch လိုအပ်သော AI/ML processors များအတွက် အရေးကြီးသော TSV (Through-Silicon Via) integration ကို ပံ့ပိုးပေးသည်။ ဥပမာအားဖြင့်၊ 25 μm အထိ thinning လုပ်ထားသော 12-inch wafers များသည် <1.5% warpage ကို ထိန်းသိမ်းထားစဉ် layer 8+ ကို stacking လုပ်ခွင့်ပြုပြီး automotive LiDAR systems များအတွက် မရှိမဖြစ်လိုအပ်ပါသည်။

• Fan-Out Packaging: wafer အထူကို 30 μm အထိ လျှော့ချခြင်းဖြင့် interconnect အရှည်ကို 50% တိုစေပြီး signal delay (<0.2 ps/mm) ကို အနည်းဆုံးဖြစ်စေပြီး မိုဘိုင်း SoC များအတွက် 0.4 mm အလွန်ပါးလွှာသော chiplet များကို ဖွင့်ပေးပါသည်။ ဤလုပ်ငန်းစဉ်သည် stress-compensated grinding algorithms များကို အသုံးပြု၍ warpage (>50 μm TTV control) ကို ကာကွယ်ပြီး မြင့်မားသော frequency RF application များတွင် ယုံကြည်စိတ်ချရမှုကို သေချာစေသည်။

၂။ ပါဝါအီလက်ထရွန်းနစ်ပစ္စည်းများ

• IGBT မော်ဂျူးများ- 50 μm အထိ ပါးလွှာစေခြင်းဖြင့် အပူခံနိုင်ရည်ကို <0.5°C/W အထိ လျော့ကျစေပြီး 1200V SiC MOSFETs များကို 200°C junction အပူချိန်များတွင် လည်ပတ်နိုင်စေပါသည်။ ကျွန်ုပ်တို့၏ စက်ပစ္စည်းများသည် မြေအောက်မျက်နှာပြင်ပျက်စီးမှုကို ဖယ်ရှားရန်အတွက် multi-stage grinding (ကြမ်းတမ်းသော- 46 μm grit → အနုစိတ်- 4 μm grit) ကို အသုံးပြုပြီး အပူလည်ပတ်မှု ယုံကြည်စိတ်ချရမှု 10,000 ကြိမ်ထက်မနည်း ရရှိစေပါသည်။ ၎င်းသည် EV inverters များအတွက် အရေးကြီးပါသည်၊ ထိုတွင် 10 μm-အထူ SiC wafers များသည် switching speed ကို 30% တိုးတက်စေပါသည်။

• GaN-on-SiC ပါဝါကိရိယာများ- 80 μm အထိ Wafer ပါးလွှာစေခြင်းသည် 650V GaN HEMTs အတွက် အီလက်ထရွန် ရွေ့လျားနိုင်စွမ်း (μ > 2000 cm²/V·s) ကို မြှင့်တင်ပေးပြီး လျှပ်ကူးမှုဆုံးရှုံးမှုများကို 18% လျှော့ချပေးသည်။ ဤလုပ်ငန်းစဉ်သည် ပါးလွှာစေစဉ် အက်ကွဲခြင်းကို ကာကွယ်ရန် လေဆာအကူအညီဖြင့် လှီးဖြတ်ထားသော အပိုင်းအစများကို အသုံးပြုပြီး RF ပါဝါချဲ့စက်များအတွက် <5 μm အနားသတ်ချစ်ပ်ခြင်းကို ရရှိစေပါသည်။

၃။ အော့ပတိုအီလက်ထရွန်းနစ်

• GaN-on-SiC LEDs: 50 μm sapphire substrates များသည် photon trapping ကို လျှော့ချခြင်းဖြင့် အလင်းထုတ်ယူမှုစွမ်းဆောင်ရည် (LEE) ကို 85% အထိ တိုးတက်ကောင်းမွန်စေသည် (150 μm wafers များအတွက် 65% နှင့် နှိုင်းယှဉ်ပါက)။ ကျွန်ုပ်တို့၏ စက်ပစ္စည်း၏ အလွန်နိမ့်သော TTV ထိန်းချုပ်မှု (<0.3 μm) သည် 12-inch wafers များတွင် တစ်ပြေးညီ LED ထုတ်လွှတ်မှုကို သေချာစေပြီး <100nm wavelength တစ်ပြေးညီဖြစ်မှု လိုအပ်သော Micro-LED display များအတွက် အရေးကြီးပါသည်။

• ဆီလီကွန် ဖိုတနစ်စ်- ၂၅μm အထူရှိသော ဆီလီကွန် ဝေဖာများသည် 1.6 Tbps optical transceiver များအတွက် မရှိမဖြစ်လိုအပ်သော waveguides များတွင် ပျံ့နှံ့မှုဆုံးရှုံးမှုကို 3 dB/cm လျော့နည်းစေသည်။ ဤလုပ်ငန်းစဉ်သည် မျက်နှာပြင်ကြမ်းတမ်းမှုကို Ra <0.1 nm အထိ လျှော့ချရန် CMP smoothing ကို ပေါင်းစပ်ထားပြီး ချိတ်ဆက်မှုစွမ်းဆောင်ရည်ကို ၄၀% မြှင့်တင်ပေးသည်။

၄။ MEMS အာရုံခံကိရိယာများ

• အရှိန်မြှင့်ကိရိယာ- ၂၅ μm ဆီလီကွန်ဝေဖာများသည် proof-mass displacement sensitivity ကို တိုးမြှင့်ခြင်းဖြင့် SNR >85 dB (50 μm ဝေဖာများအတွက် 75 dB vs.) ကို ရရှိစေသည်။ ကျွန်ုပ်တို့၏ dual-axis grindingစနစ်သည် stress gradient များကို ပြန်လည်ဖြည့်ဆည်းပေးပြီး -40°C မှ 125°C အတွင်း <0.5% sensitivity drift ကို သေချာစေသည်။ အသုံးချမှုများတွင် မော်တော်ကားတိုက်မှု ထောက်လှမ်းခြင်းနှင့် AR/VR ရွေ့လျားမှု ခြေရာခံခြင်းတို့ ပါဝင်သည်။

• ဖိအားအာရုံခံကိရိယာများ- 40 μm အထိပါးလွှာစေခြင်းဖြင့် <0.1% FS hysteresis ဖြင့် 0–300 bar တိုင်းတာမှုအကွာအဝေးများကို ဖြစ်စေသည်။ ယာယီချည်နှောင်မှု (ဖန်သယ်ဆောင်သူများ) ကို အသုံးပြုခြင်းဖြင့် လုပ်ငန်းစဉ်သည် backside etching အတွင်း wafer ကျိုးခြင်းကို ရှောင်ရှားပြီး စက်မှုလုပ်ငန်း IoT အာရုံခံကိရိယာများအတွက် ဖိအားလွန်ကဲမှုခံနိုင်ရည် <1 μm ကို ရရှိစေပါသည်။

• နည်းပညာဆိုင်ရာ ပေါင်းစပ်စွမ်းအား- ကျွန်ုပ်တို့၏ wafer thinning စက်ကိရိယာများသည် မတူညီသော ပစ္စည်းစိန်ခေါ်မှုများ (Si၊ SiC၊ Sapphire) ကို ဖြေရှင်းရန် စက်ပိုင်းဆိုင်ရာ grinding၊ CMP နှင့် plasma etching တို့ကို ပေါင်းစည်းပေးပါသည်။ ဥပမာအားဖြင့်၊ GaN-on-SiC သည် မာကျောမှုနှင့် အပူချဲ့ထွင်မှုကို ဟန်ချက်ညီစေရန် hybrid grinding (စိန်ဘီးများ + plasma) လိုအပ်ပြီး MEMS အာရုံခံကိရိယာများသည် CMP polishing မှတစ်ဆင့် 5 nm အောက် မျက်နှာပြင်ကြမ်းတမ်းမှုကို တောင်းဆိုပါသည်။

• စက်မှုလုပ်ငန်းအပေါ် သက်ရောက်မှု- ပိုမိုပါးလွှာပြီး စွမ်းဆောင်ရည်မြင့်မားသော ဝေဖာများကို ဖန်တီးခြင်းဖြင့် ဤနည်းပညာသည် AI ချစ်ပ်များ၊ 5G mmWave မော်ဂျူးများနှင့် ပြောင်းလွယ်ပြင်လွယ်ရှိသော အီလက်ထရွန်းနစ်ပစ္စည်းများတွင် ဆန်းသစ်တီထွင်မှုများကို မောင်းနှင်ပေးပြီး ခေါက်နိုင်သော မျက်နှာပြင်များအတွက် TTV ခံနိုင်ရည် <0.1 μm နှင့် မော်တော်ကား LiDAR အာရုံခံကိရိယာများအတွက် <0.5 μm တို့ ပါဝင်သည်။

XKH ရဲ့ ဝန်ဆောင်မှုတွေ

၁။ စိတ်ကြိုက်ဖြေရှင်းချက်များ

တိုးချဲ့နိုင်သော ဖွဲ့စည်းမှုပုံစံများ- အလိုအလျောက် တင်/ချသည့် ၄-၁၂ လက်မ အခန်းဒီဇိုင်းများ။

Doping အထောက်အပံ့- Er/Yb-doped crystals များနှင့် InP/GaAs wafers များအတွက် စိတ်ကြိုက်ချက်ပြုတ်နည်းများ။

၂။ အစမှအဆုံး ပံ့ပိုးမှု

လုပ်ငန်းစဉ် ဖွံ့ဖြိုးတိုးတက်ရေး- အကောင်းဆုံးဖြစ်အောင် ပြုလုပ်ခြင်းဖြင့် အခမဲ့ အစမ်းသုံးနိုင်ပါသည်။

ကမ္ဘာလုံးဆိုင်ရာ လေ့ကျင့်ရေး- ပြုပြင်ထိန်းသိမ်းမှုနှင့် ပြဿနာရှာဖွေဖြေရှင်းခြင်းဆိုင်ရာ နှစ်စဉ် နည်းပညာဆိုင်ရာ အလုပ်ရုံဆွေးနွေးပွဲများ။

၃။ ပစ္စည်းပေါင်းစုံ စီမံဆောင်ရွက်ခြင်း

SiC: Ra <0.1 nm ဖြင့် 100 μm အထိ ပါးလွှာသော ဝေဖာ။

နီလာရောင်: UV လေဆာပြတင်းပေါက်များအတွက် 50μm အထူ (transmittance >92%@200 nm)။

၄။ တန်ဖိုးမြှင့်ဝန်ဆောင်မှုများ

စားသုံးနိုင်သော ထောက်ပံ့ရေးပစ္စည်း- စိန်ဘီးများ (သက်တမ်းတစ်ခုလျှင် ဝေဖာ ၂၀၀၀+) နှင့် CMP အရည်ပျော်ပစ္စည်းများ။

နိဂုံးချုပ်

ဤ wafer thinning စက်သည် လုပ်ငန်းနယ်ပယ်တွင် ဦးဆောင်နေသော တိကျမှု၊ ဘက်စုံသုံးနိုင်သော ပစ္စည်းများနှင့် စမတ်အလိုအလျောက်လုပ်ဆောင်မှုများကို ပေးစွမ်းပြီး 3D ပေါင်းစပ်မှုနှင့် ပါဝါအီလက်ထရွန်းနစ်ပစ္စည်းများအတွက် မရှိမဖြစ်လိုအပ်ပါသည်။ XKH ၏ ပြည့်စုံသောဝန်ဆောင်မှုများ—စိတ်ကြိုက်ပြင်ဆင်ခြင်းမှသည် post-processing အထိ—သည် သုံးစွဲသူများအား semiconductor ထုတ်လုပ်ရာတွင် ကုန်ကျစရိတ်သက်သာမှုနှင့် စွမ်းဆောင်ရည်ထူးချွန်မှုကို ရရှိစေကြောင်း သေချာစေပါသည်။