တစ်ပိုင်းလျှပ်ကူးပစ္စည်းလုပ်ငန်း၏ ဖွံ့ဖြိုးတိုးတက်မှု မြန်ဆန်သော လုပ်ငန်းစဉ်တွင်၊ ඔප දැමී ...တစ်ခုတည်းသော ပုံဆောင်ခဲများဆီလီကွန်ဝေဖာများအရေးပါသော အခန်းကဏ္ဍမှ ပါဝင်သည်။ ၎င်းတို့သည် မိုက်ခရိုအီလက်ထရွန်းနစ် စက်ပစ္စည်းအမျိုးမျိုး ထုတ်လုပ်ရာတွင် အခြေခံပစ္စည်းအဖြစ် ဆောင်ရွက်သည်။ ရှုပ်ထွေးပြီး တိကျသော ပေါင်းစပ်ဆားကစ်များမှသည် မြန်နှုန်းမြင့် မိုက်ခရိုပရိုဆက်ဆာများနှင့် ဘက်စုံသုံး အာရုံခံကိရိယာများအထိ၊ ඔප දැමීමීමတစ်ခုတည်းသော ပုံဆောင်ခဲများအထိဆီလီကွန်ဝေဖာများတို့သည် မရှိမဖြစ်လိုအပ်ပါသည်။ ၎င်းတို့၏ စွမ်းဆောင်ရည်နှင့် သတ်မှတ်ချက်များတွင် ကွာခြားချက်များသည် နောက်ဆုံးထုတ်ကုန်များ၏ အရည်အသွေးနှင့် စွမ်းဆောင်ရည်ကို တိုက်ရိုက်အကျိုးသက်ရောက်စေပါသည်။ အောက်တွင် ඔප දැමීම single crystal silicon wafers များ၏ အဖြစ်များသော သတ်မှတ်ချက်များနှင့် parameters များ ဖော်ပြထားပါသည်-

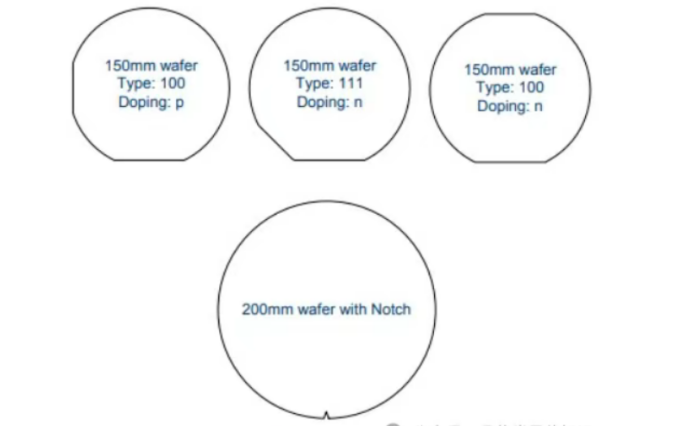

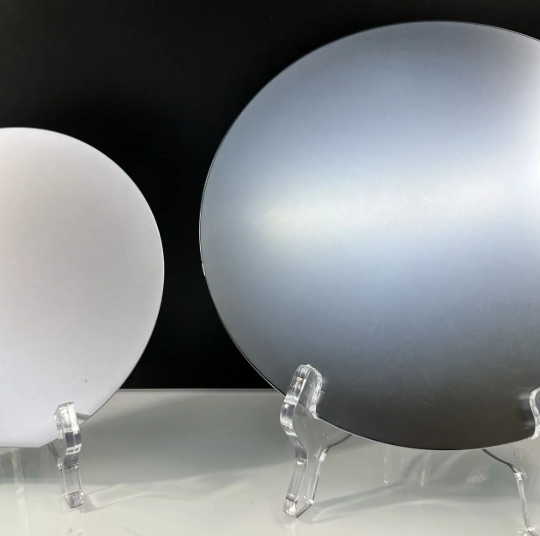

အချင်း: semiconductor single crystal silicon wafers များ၏ အရွယ်အစားကို ၎င်းတို့၏ အချင်းဖြင့် တိုင်းတာပြီး သတ်မှတ်ချက်များ အမျိုးမျိုးဖြင့် ရရှိနိုင်ပါသည်။ အသုံးများသော အချင်းများတွင် ၂ လက်မ (၅၀.၈ မီလီမီတာ)၊ ၃ လက်မ (၇၆.၂ မီလီမီတာ)၊ ၄ လက်မ (၁၀၀ မီလီမီတာ)၊ ၅ လက်မ (၁၂၅ မီလီမီတာ)၊ ၆ လက်မ (၁၅၀ မီလီမီတာ)၊ ၈ လက်မ (၂၀၀ မီလီမီတာ)၊ ၁၂ လက်မ (၃၀၀ မီလီမီတာ) နှင့် ၁၈ လက်မ (၄၅၀ မီလီမီတာ) တို့ ပါဝင်သည်။ အချင်းအမျိုးမျိုးသည် ထုတ်လုပ်မှုလိုအပ်ချက်များနှင့် လုပ်ငန်းစဉ်လိုအပ်ချက်အမျိုးမျိုးအတွက် သင့်လျော်ပါသည်။ ဥပမာအားဖြင့်၊ အချင်းသေးငယ်သော wafers များကို အထူး၊ ပမာဏသေးငယ်သော မိုက်ခရိုအီလက်ထရွန်းနစ် စက်ပစ္စည်းများအတွက် အသုံးများပြီး အချင်းကြီးမားသော wafers များသည် ကြီးမားသော integrated circuit ထုတ်လုပ်ရာတွင် ထုတ်လုပ်မှုထိရောက်မှုနှင့် ကုန်ကျစရိတ်အားသာချက်များကို ပြသသည်။ မျက်နှာပြင်လိုအပ်ချက်များကို single-side polished (SSP) နှင့် double-side polished (DSP) အဖြစ် အမျိုးအစားခွဲခြားထားသည်။ single-side polished wafers များကို sensor အချို့ကဲ့သို့ တစ်ဖက်တွင် ပြားချပ်ချပ်မြင့်မားသော စက်ပစ္စည်းများအတွက် အသုံးပြုသည်။ Double-side polished wafers များကို မျက်နှာပြင်နှစ်ခုလုံးတွင် တိကျမှုမြင့်မားသော integrated circuits များနှင့် အခြားထုတ်ကုန်များအတွက် အသုံးများသည်။ မျက်နှာပြင်လိုအပ်ချက် (အပြီးသတ်): တစ်ဖက်တစ်ချက် ඔප දැමීම SSP / နှစ်ဖက် ඔප දැමීම DSP။

အမျိုးအစား/Dopant: (1) N-type Semiconductor: အချို့သော မသန့်စင်သော အက်တမ်များကို intrinsic semiconductor ထဲသို့ ထည့်သွင်းသောအခါ၊ ၎င်းတို့သည် ၎င်း၏ conductivity ကို ပြောင်းလဲစေသည်။ ဥပမာအားဖြင့်၊ နိုက်ထရိုဂျင် (N)၊ ဖော့စဖရပ်စ် (P)၊ အာဆင်းနစ် (As) သို့မဟုတ် antimony (Sb) ကဲ့သို့သော pentavalent ဒြပ်စင်များကို ထည့်သွင်းသောအခါ၊ ၎င်းတို့၏ valence electrons များသည် ပတ်ဝန်းကျင် silicon အက်တမ်များ၏ valence electrons များနှင့် covalent bond များကို ဖွဲ့စည်းပြီး covalent bond ဖြင့် မချည်နှောင်ထားသော အပို electron တစ်ခုကို ချန်ထားခဲ့သည်။ ၎င်းသည် hole concentration ထက် ပိုမိုမြင့်မားသော electron concentration ကို ဖြစ်ပေါ်စေပြီး electron-type semiconductor အဖြစ်လည်း လူသိများသော N-type semiconductor ကို ဖွဲ့စည်းပေးသည်။ N-type semiconductor များသည် အချို့သော power devices များကဲ့သို့ electrons များကို အဓိက charge carriers အဖြစ် လိုအပ်သော devices များ ထုတ်လုပ်ရာတွင် အရေးပါပါသည်။ (2) P-type Semiconductor: boron (B)၊ gallium (Ga) သို့မဟုတ် indium (In) ကဲ့သို့သော trivalent မသန့်စင်သော ဒြပ်စင်များကို silicon semiconductor ထဲသို့ ထည့်သွင်းသောအခါ၊ မသန့်စင်သော အက်တမ်များ၏ valence electrons များသည် ပတ်ဝန်းကျင် silicon အက်တမ်များနှင့် covalent bond များကို ဖွဲ့စည်းသော်လည်း၊ ၎င်းတို့တွင် valence electron အနည်းဆုံး တစ်ခု ချို့တဲ့ပြီး covalent bond အပြည့်အစုံကို မဖွဲ့စည်းနိုင်ပါ။ ၎င်းက အီလက်ထရွန်ပါဝင်မှုထက် အပေါက်ပါဝင်မှုပိုများစေပြီး P-type semiconductor ကို hole-type semiconductor အဖြစ်လည်းလူသိများသည်။ P-type semiconductor များသည် ဒိုင်အိုဒိုက်များနှင့် ထရန်စစ္စတာအချို့ကဲ့သို့သော အပေါက်များသည် အဓိကအားသွင်းသယ်ဆောင်သူများအဖြစ် ဆောင်ရွက်သည့် စက်ပစ္စည်းများ ထုတ်လုပ်ရာတွင် အဓိကအခန်းကဏ္ဍမှ ပါဝင်သည်။

ခုခံမှု- ခုခံမှုသည် ඔප දැමීම single crystal silicon wafers များ၏ လျှပ်စစ်စီးကူးမှုကို တိုင်းတာသည့် အဓိက ရုပ်ပိုင်းဆိုင်ရာ ပမာဏတစ်ခုဖြစ်သည်။ ၎င်း၏တန်ဖိုးသည် ပစ္စည်း၏ လျှပ်ကူးနိုင်စွမ်းကို ထင်ဟပ်စေသည်။ ခုခံမှုနည်းလေ၊ silicon wafer ၏ လျှပ်ကူးနိုင်စွမ်း ပိုကောင်းလေဖြစ်သည်။ ဆန့်ကျင်ဘက်အားဖြင့် ခုခံမှုမြင့်လေ၊ လျှပ်ကူးနိုင်စွမ်း ညံ့လေဖြစ်သည်။ silicon wafers များ၏ ခုခံမှုကို ၎င်းတို့၏ မွေးရာပါ ပစ္စည်းဂုဏ်သတ္တိများဖြင့် ဆုံးဖြတ်ပြီး အပူချိန်သည်လည်း သိသာထင်ရှားသော သက်ရောက်မှုရှိသည်။ ယေဘုယျအားဖြင့် silicon wafers များ၏ ခုခံမှုသည် အပူချိန်နှင့်အတူ တိုးလာသည်။ လက်တွေ့အသုံးချမှုများတွင် မတူညီသော microelectronic devices များတွင် silicon wafers များအတွက် ခုခံမှုလိုအပ်ချက်များ မတူညီပါ။ ဥပမာအားဖြင့်၊ integrated circuit ထုတ်လုပ်ရာတွင် အသုံးပြုသော wafers များသည် တည်ငြိမ်ပြီး ယုံကြည်စိတ်ချရသော device စွမ်းဆောင်ရည်ကို သေချာစေရန်အတွက် ခုခံမှု၏ တိကျသောထိန်းချုပ်မှု လိုအပ်ပါသည်။

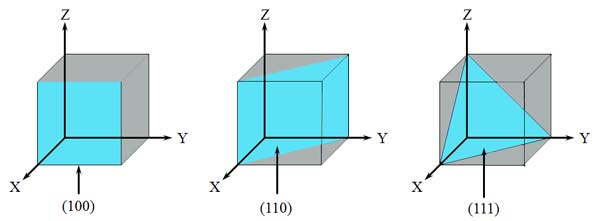

ဦးတည်ချက်- ဝေဖာ၏ ပုံဆောင်ခဲ ဦးတည်ချက်သည် ဆီလီကွန်ကွက်တိပ်၏ ပုံဆောင်ခဲ ဦးတည်ချက်ကို ကိုယ်စားပြုပြီး ပုံမှန်အားဖြင့် (100)၊ (110)၊ (111) စသည်ဖြင့် မီလာအညွှန်းကိန်းများဖြင့် သတ်မှတ်ထားသည်။ မတူညီသော ပုံဆောင်ခဲ ဦးတည်ချက်များတွင် ဦးတည်ချက်ပေါ် မူတည်၍ ကွဲပြားသော လိုင်းသိပ်သည်းဆကဲ့သို့သော မတူညီသော ရုပ်ပိုင်းဆိုင်ရာ ဂုဏ်သတ္တိများရှိသည်။ ဤကွာခြားချက်သည် နောက်ဆက်တွဲ လုပ်ဆောင်မှုအဆင့်များတွင် ဝေဖာ၏ စွမ်းဆောင်ရည်နှင့် မိုက်ခရိုအီလက်ထရွန်းနစ် စက်ပစ္စည်းများ၏ နောက်ဆုံးစွမ်းဆောင်ရည်ကို ထိခိုက်စေနိုင်သည်။ ထုတ်လုပ်မှုလုပ်ငန်းစဉ်တွင် မတူညီသော စက်ပစ္စည်းလိုအပ်ချက်များအတွက် သင့်လျော်သော ဦးတည်ချက်ရှိသော ဆီလီကွန်ဝေဖာကို ရွေးချယ်ခြင်းသည် စက်ပစ္စည်းစွမ်းဆောင်ရည်ကို အကောင်းဆုံးဖြစ်အောင် လုပ်ဆောင်ပေးနိုင်ခြင်း၊ ထုတ်လုပ်မှုစွမ်းဆောင်ရည်ကို တိုးတက်ကောင်းမွန်စေပြီး ထုတ်ကုန်အရည်အသွေးကို မြှင့်တင်ပေးနိုင်သည်။

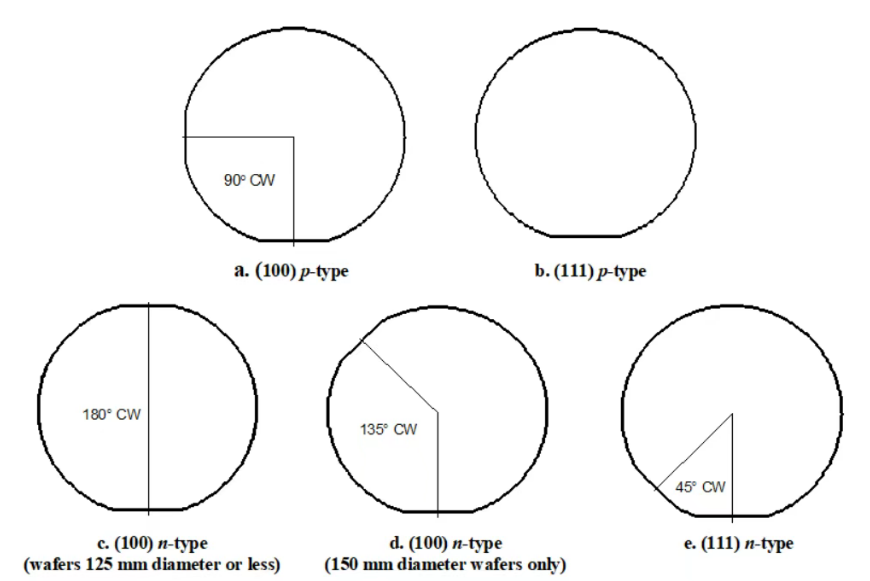

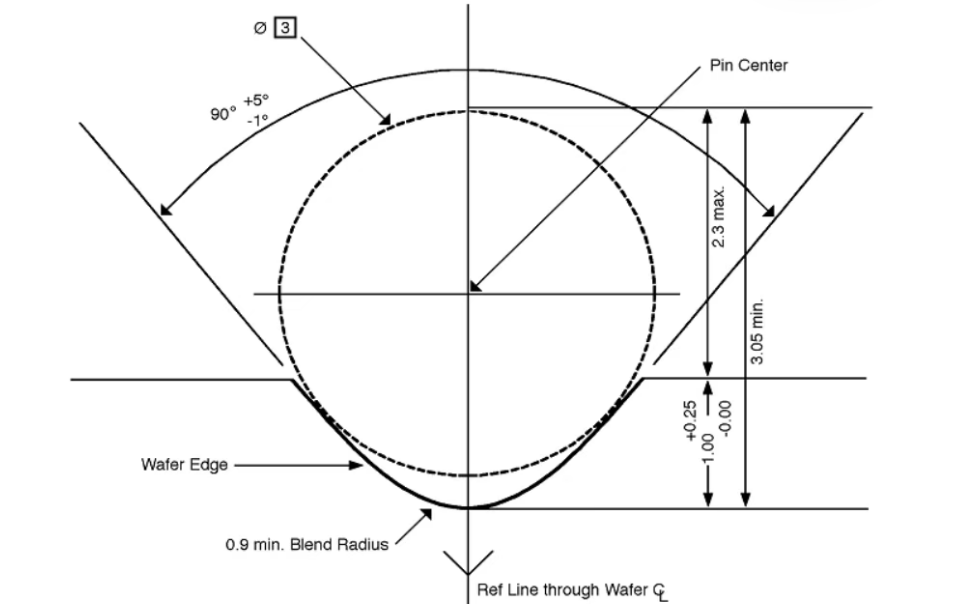

Flat/Notch: ဆီလီကွန်ဝေဖာ၏ အဝန်းရှိ flat edge (Flat) သို့မဟုတ် V-notch (Notch) သည် crystal orientation alignment တွင် အရေးပါသော အခန်းကဏ္ဍမှ ပါဝင်ပြီး ဝေဖာ ထုတ်လုပ်ခြင်းနှင့် လုပ်ဆောင်ခြင်းတွင် အရေးကြီးသော အမှတ်အသားတစ်ခုဖြစ်သည်။ အချင်းအမျိုးမျိုးရှိသော ဝေဖာများသည် Flat သို့မဟုတ် Notch ၏ အရှည်အတွက် မတူညီသော စံနှုန်းများနှင့် ကိုက်ညီသည်။ alignment edge များကို primary flat နှင့် secondary flat အဖြစ် ခွဲခြားထားသည်။ primary flat ကို wafer ၏ အခြေခံ crystal orientation နှင့် processing reference ကို ဆုံးဖြတ်ရန် အဓိကအသုံးပြုပြီး secondary flat သည် တိကျသော alignment နှင့် processing တွင် ပိုမိုကူညီပေးပြီး ထုတ်လုပ်မှုလိုင်းတစ်လျှောက် wafer ၏ တိကျသောလည်ပတ်မှုနှင့် တသမတ်တည်းရှိမှုကို သေချာစေသည်။

အထူ: ဝေဖာ၏အထူကို မိုက်ခရိုမီတာ (μm) ဖြင့် သတ်မှတ်ထားပြီး အထူမှာ 100μm မှ 1000μm အကြားတွင် ရှိသည်။ အထူအမျိုးမျိုးရှိသော ဝေဖာများသည် မိုက်ခရိုအီလက်ထရွန်းနစ် စက်ပစ္စည်းအမျိုးအစား အမျိုးမျိုးအတွက် သင့်လျော်သည်။ ပိုပါးသော ဝေဖာများ (ဥပမာ 100μm – 300μm) ကို တင်းကျပ်သော အထူထိန်းချုပ်မှု လိုအပ်သည့် ချစ်ပ်ထုတ်လုပ်မှုအတွက်၊ ချစ်ပ်၏ အရွယ်အစားနှင့် အလေးချိန်ကို လျှော့ချရန်နှင့် ပေါင်းစပ်သိပ်သည်းဆကို တိုးမြှင့်ရန်အတွက် မကြာခဏ အသုံးပြုလေ့ရှိသည်။ ပိုထူသော ဝေဖာများ (ဥပမာ 500μm – 1000μm) ကို လည်ပတ်နေစဉ်အတွင်း တည်ငြိမ်မှုရှိစေရန်အတွက် ပါဝါတစ်ပိုင်းလျှပ်ကူးပစ္စည်းများကဲ့သို့သော စက်ပိုင်းဆိုင်ရာအစွမ်းသတ္တိ မြင့်မားရန် လိုအပ်သည့် စက်ပစ္စည်းများတွင် ကျယ်ကျယ်ပြန့်ပြန့် အသုံးပြုကြသည်။

မျက်နှာပြင်ကြမ်းတမ်းမှု- မျက်နှာပြင်ကြမ်းတမ်းမှုသည် wafer အရည်အသွေးကို အကဲဖြတ်ရာတွင် အဓိက parameter များထဲမှ တစ်ခုဖြစ်ပြီး၊ wafer နှင့် နောက်ပိုင်းတွင် စုပုံထားသော ပါးလွှာသောဖလင်ပစ္စည်းများအကြား ကပ်ငြိမှုအပြင် စက်ပစ္စည်း၏ လျှပ်စစ်စွမ်းဆောင်ရည်ကို တိုက်ရိုက်အကျိုးသက်ရောက်စေသောကြောင့်ဖြစ်သည်။ ၎င်းကို root mean square (RMS) ကြမ်းတမ်းမှု (nm ဖြင့်) အဖြစ် ဖော်ပြလေ့ရှိသည်။ မျက်နှာပြင်ကြမ်းတမ်းမှုနည်းခြင်းသည် wafer မျက်နှာပြင်ချောမွေ့သည်ဟု ဆိုလိုပြီး အီလက်ထရွန်ပြန့်ကျဲမှုကဲ့သို့သော ဖြစ်စဉ်များကို လျှော့ချရန်နှင့် စက်ပစ္စည်းစွမ်းဆောင်ရည်နှင့် ယုံကြည်စိတ်ချရမှုကို တိုးတက်စေရန် ကူညီပေးသည်။ အဆင့်မြင့် semiconductor ထုတ်လုပ်မှုလုပ်ငန်းစဉ်များတွင် မျက်နှာပြင်ကြမ်းတမ်းမှုလိုအပ်ချက်များသည် ပိုမိုတင်းကျပ်လာနေပြီး အထူးသဖြင့် မျက်နှာပြင်ကြမ်းတမ်းမှုကို နာနိုမီတာအနည်းငယ် သို့မဟုတ် ထို့ထက်နိမ့်သောအဆင့်အထိ ထိန်းချုပ်ရမည့် high-end integrated circuit ထုတ်လုပ်မှုအတွက် ပိုမိုတင်းကျပ်လာပါသည်။

စုစုပေါင်းအထူပြောင်းလဲမှု (TTV): စုစုပေါင်းအထူပြောင်းလဲမှုဆိုသည်မှာ wafer မျက်နှာပြင်ပေါ်ရှိ အမှတ်များစွာတွင် တိုင်းတာထားသော အများဆုံးနှင့် အနည်းဆုံးအထူများအကြား ကွာခြားချက်ကို ရည်ညွှန်းပြီး ပုံမှန်အားဖြင့် μm ဖြင့်ဖော်ပြသည်။ TTV မြင့်မားခြင်းသည် photolithography နှင့် etching ကဲ့သို့သော လုပ်ငန်းစဉ်များတွင် သွေဖည်မှုများကို ဖြစ်ပေါ်စေနိုင်ပြီး စက်ပစ္စည်းစွမ်းဆောင်ရည် တသမတ်တည်းရှိမှုနှင့် အထွက်နှုန်းကို ထိခိုက်စေနိုင်သည်။ ထို့ကြောင့် wafer ထုတ်လုပ်စဉ် TTV ကို ထိန်းချုပ်ခြင်းသည် ထုတ်ကုန်အရည်အသွေးကို သေချာစေရန် အဓိကခြေလှမ်းတစ်ခုဖြစ်သည်။ မြင့်မားသော တိကျမှုရှိသော မိုက်ခရိုအီလက်ထရွန်းနစ် စက်ပစ္စည်း ထုတ်လုပ်ရန်အတွက် TTV သည် ပုံမှန်အားဖြင့် မိုက်ခရိုမီတာအနည်းငယ်အတွင်း ရှိရန် လိုအပ်ပါသည်။

ကွေးညွှတ်ခြင်း- ကွေးညွှတ်ခြင်းဆိုသည်မှာ ဝေဖာမျက်နှာပြင်နှင့် အကောင်းဆုံးပြားချပ်ချပ်မျက်နှာပြင်အကြား သွေဖည်မှုကို ရည်ညွှန်းပြီး ပုံမှန်အားဖြင့် μm ဖြင့် တိုင်းတာသည်။ အလွန်အကျွံကွေးညွှတ်နေသော ဝေဖာများသည် နောက်ဆက်တွဲ လုပ်ငန်းစဉ်အတွင်း ကျိုးပဲ့ခြင်း သို့မဟုတ် မညီမျှသောဖိအားကို ကြုံတွေ့ရနိုင်ပြီး ထုတ်လုပ်မှုထိရောက်မှုနှင့် ထုတ်ကုန်အရည်အသွေးကို ထိခိုက်စေပါသည်။ အထူးသဖြင့် ဖိုတိုလစ်သိုဂရပ်ဖီကဲ့သို့သော မြင့်မားသောပြားချပ်ချပ်လိုအပ်သည့် လုပ်ငန်းစဉ်များတွင် ဖိုတိုလစ်သိုဂရပ်ဖီပုံစံ၏ တိကျမှုနှင့် တသမတ်တည်းရှိမှုကို သေချာစေရန် ကွေးညွှတ်ခြင်းကို သတ်မှတ်ထားသော အတိုင်းအတာအတွင်း ထိန်းချုပ်ရမည်။

ဝါ့ပ်- ဝါ့ပ်သည် ဝေဖာမျက်နှာပြင်နှင့် အကောင်းဆုံးလုံးပုံသဏ္ဍာန်အကြား သွေဖည်မှုကို ညွှန်ပြပြီး μm ဖြင့်လည်း တိုင်းတာသည်။ ဘောင်နှင့်ဆင်တူစွာ၊ ဝါ့ပ်သည် ဝေဖာပြားချပ်ချပ်၏ အရေးကြီးသော အညွှန်းကိန်းတစ်ခုဖြစ်သည်။ ဝါ့ပ်လွန်ကဲခြင်းသည် လုပ်ငန်းစဉ်စက်ပစ္စည်းများတွင် ဝေဖာ၏ နေရာချထားမှုတိကျမှုကို ထိခိုက်စေရုံသာမက ချစ်ပ်ထုပ်ပိုးမှုလုပ်ငန်းစဉ်အတွင်း ချစ်ပ်နှင့်ထုပ်ပိုးပစ္စည်းအကြား ချိတ်ဆက်မှုညံ့ဖျင်းခြင်းကဲ့သို့သော ပြဿနာများကိုပါ ဖြစ်စေနိုင်ပြီး ၎င်းသည် စက်ပစ္စည်း၏ယုံကြည်စိတ်ချရမှုကို ထိခိုက်စေပါသည်။ အဆင့်မြင့်တစ်ပိုင်းလျှပ်ကူးပစ္စည်းထုတ်လုပ်မှုတွင်၊ အဆင့်မြင့်ချစ်ပ်ထုတ်လုပ်မှုနှင့်ထုပ်ပိုးမှုလုပ်ငန်းစဉ်များ၏ လိုအပ်ချက်များကို ဖြည့်ဆည်းရန် ဝါ့ပ်လိုအပ်ချက်များသည် ပိုမိုတင်းကျပ်လာပါသည်။

အစွန်းပရိုဖိုင်- ဝေဖာ၏ အစွန်းပရိုဖိုင်သည် ၎င်း၏နောက်ဆက်တွဲ လုပ်ဆောင်မှုနှင့် ကိုင်တွယ်မှုအတွက် အရေးကြီးပါသည်။ ၎င်းကို ပုံမှန်အားဖြင့် အစွန်းဖယ်ထုတ်ဇုန် (EEZ) ဖြင့် သတ်မှတ်ထားပြီး ၎င်းသည် လုပ်ဆောင်ခွင့်မပြုသည့် ဝေဖာအစွန်းမှ အကွာအဝေးကို သတ်မှတ်ပေးသည်။ ကောင်းမွန်စွာ ဒီဇိုင်းထုတ်ထားသော အစွန်းပရိုဖိုင်နှင့် တိကျသော EEZ ထိန်းချုပ်မှုသည် လုပ်ဆောင်နေစဉ်အတွင်း အစွန်းချို့ယွင်းချက်များ၊ ဖိစီးမှုအာရုံစူးစိုက်မှုများနှင့် အခြားပြဿနာများကို ရှောင်ရှားရန် ကူညီပေးပြီး ဝေဖာအရည်အသွေးနှင့် အထွက်နှုန်းကို တိုးတက်ကောင်းမွန်စေသည်။ အဆင့်မြင့်ထုတ်လုပ်မှုလုပ်ငန်းစဉ်အချို့တွင် အစွန်းပရိုဖိုင်တိကျမှုသည် sub-micron အဆင့်တွင် ရှိရန် လိုအပ်ပါသည်။

အမှုန်အရေအတွက်- ဝေဖာမျက်နှာပြင်ပေါ်ရှိ အမှုန်များ၏ အရေအတွက်နှင့် အရွယ်အစားဖြန့်ဖြူးမှုသည် မိုက်ခရိုအီလက်ထရွန်းနစ်ကိရိယာများ၏ စွမ်းဆောင်ရည်ကို သိသိသာသာ သက်ရောက်မှုရှိသည်။ အမှုန်များ အလွန်အကျွံ သို့မဟုတ် ကြီးမားခြင်းသည် ကိရိယာချို့ယွင်းမှုများ၊ ဥပမာ ရှော့ပတ်လမ်း သို့မဟုတ် ယိုစိမ့်မှုတို့ကို ဖြစ်စေနိုင်ပြီး ထုတ်ကုန်အထွက်နှုန်းကို လျော့ကျစေနိုင်သည်။ ထို့ကြောင့် အမှုန်အရေအတွက်ကို 0.3μm ထက်ပိုကြီးသော အမှုန်အရေအတွက်ကဲ့သို့သော ယူနစ်ဧရိယာတစ်ခုလျှင် အမှုန်များကို ရေတွက်ခြင်းဖြင့် တိုင်းတာလေ့ရှိသည်။ ဝေဖာထုတ်လုပ်မှုအတွင်း အမှုန်အရေအတွက်ကို တင်းကျပ်စွာထိန်းချုပ်ခြင်းသည် ထုတ်ကုန်အရည်အသွေးကို သေချာစေရန် မရှိမဖြစ်လိုအပ်သော တိုင်းတာမှုတစ်ခုဖြစ်သည်။ ဝေဖာမျက်နှာပြင်ပေါ်ရှိ အမှုန်ညစ်ညမ်းမှုကို လျှော့ချရန်အတွက် အဆင့်မြင့်သန့်ရှင်းရေးနည်းပညာများနှင့် သန့်ရှင်းသောထုတ်လုပ်မှုပတ်ဝန်းကျင်ကို အသုံးပြုထားသည်။

![]()

![]()

![]()

![]()

![]()

ဆက်စပ်ထုတ်လုပ်မှု

တစ်ခုတည်းသော ပုံဆောင်ခဲ ဆီလီကွန် ဝေဖာ Si အလွှာအမျိုးအစား N/P ရွေးချယ်နိုင်သော ဆီလီကွန် ကာဗိုက် ဝေဖာ

FZ CZ Si wafer စတော့ရှယ်ယာတွင်ရှိသည် 12 လက်မ Silicon wafer Prime သို့မဟုတ် Test

ပို့စ်တင်ချိန်: ၂၀၂၅ ခုနှစ်၊ ဧပြီလ ၁၈ ရက်