တတိယမျိုးဆက် တစ်ပိုင်းလျှပ်ကူးပစ္စည်းအဖြစ်၊ဆီလီကွန်ကာဗိုက် (SiC)single crystal သည် မြင့်မားသောကြိမ်နှုန်းနှင့် မြင့်မားသောပါဝါအီလက်ထရွန်းနစ်ကိရိယာများထုတ်လုပ်ရာတွင် ကျယ်ပြန့်သောအသုံးချမှုအလားအလာများရှိသည်။ SiC ၏လုပ်ဆောင်ခြင်းနည်းပညာသည် အရည်အသွေးမြင့် substrate ပစ္စည်းများထုတ်လုပ်မှုတွင် အဆုံးအဖြတ်ပေးသောအခန်းကဏ္ဍမှ ပါဝင်သည်။ ဤဆောင်းပါးသည် တရုတ်နိုင်ငံနှင့် ပြည်ပရှိ SiC လုပ်ဆောင်ခြင်းနည်းပညာများဆိုင်ရာ သုတေသန၏လက်ရှိအခြေအနေကို မိတ်ဆက်ပေးထားပြီး၊ ဖြတ်တောက်ခြင်း၊ ကြိတ်ခြင်းနှင့် ඔප දැමීමလုပ်ငန်းစဉ်များ၏ယန္တရားများအပြင် wafer ပြားချပ်မှုနှင့် မျက်နှာပြင်ကြမ်းတမ်းမှုတို့၏ခေတ်ရေစီးကြောင်းများကို ခွဲခြမ်းစိတ်ဖြာခြင်းနှင့် နှိုင်းယှဉ်ခြင်းတို့ပါဝင်သည်။ ၎င်းသည် SiC wafer လုပ်ဆောင်ခြင်းတွင် လက်ရှိစိန်ခေါ်မှုများကိုလည်း ထောက်ပြပြီး အနာဂတ်ဖွံ့ဖြိုးတိုးတက်မှုဦးတည်ချက်များကို ဆွေးနွေးထားသည်။

ဆီလီကွန်ကာဗိုက် (SiC)ဝေဖာများသည် တတိယမျိုးဆက် semiconductor စက်ပစ္စည်းများအတွက် အရေးကြီးသော အခြေခံပစ္စည်းများဖြစ်ပြီး မိုက်ခရိုအီလက်ထရွန်းနစ်၊ ပါဝါအီလက်ထရွန်းနစ်နှင့် semiconductor မီးအလင်းရောင်ကဲ့သို့သော နယ်ပယ်များတွင် သိသာထင်ရှားသော အရေးပါမှုနှင့် ဈေးကွက်အလားအလာရှိသည်။ အလွန်မြင့်မားသော မာကျောမှုနှင့် ဓာတုဗေဒဆိုင်ရာ တည်ငြိမ်မှုကြောင့်SiC တစ်ပိုင်းပုံဆောင်ခဲများရိုးရာ semiconductor processing နည်းလမ်းများသည် ၎င်းတို့၏ စက်ဖြင့်ပြုပြင်ခြင်းအတွက် လုံးဝသင့်လျော်မှုမရှိပါ။ နိုင်ငံတကာကုမ္ပဏီများစွာသည် SiC single crystals များ၏ နည်းပညာပိုင်းဆိုင်ရာ လိုအပ်ချက်များသော processing တွင် ကျယ်ကျယ်ပြန့်ပြန့် သုတေသနပြုလုပ်ခဲ့သော်လည်း၊ သက်ဆိုင်ရာနည်းပညာများကို လျှို့ဝှက်ထားရှိပါသည်။

မကြာသေးမီနှစ်များအတွင်း တရုတ်နိုင်ငံသည် SiC single crystal ပစ္စည်းများနှင့် စက်ပစ္စည်းများ ဖွံ့ဖြိုးတိုးတက်ရေးတွင် ကြိုးပမ်းအားထုတ်မှုများကို တိုးမြှင့်လုပ်ဆောင်ခဲ့သည်။ သို့သော် နိုင်ငံအတွင်း SiC စက်ပစ္စည်းနည်းပညာ တိုးတက်မှုသည် လက်ရှိတွင် လုပ်ငန်းစဉ်နည်းပညာများနှင့် wafer အရည်အသွေးတို့တွင် ကန့်သတ်ချက်များကြောင့် အကန့်အသတ်ရှိနေသည်။ ထို့ကြောင့် SiC single crystal substrates များ၏ အရည်အသွေးကို မြှင့်တင်ရန်နှင့် ၎င်းတို့၏ လက်တွေ့အသုံးချမှုနှင့် အစုလိုက်အပြုံလိုက်ထုတ်လုပ်မှုကို အောင်မြင်စေရန် SiC လုပ်ငန်းစဉ်စွမ်းရည်များကို မြှင့်တင်ရန် တရုတ်နိုင်ငံအတွက် အရေးကြီးပါသည်။

အဓိက လုပ်ဆောင်သည့် အဆင့်များတွင် အောက်ပါတို့ ပါဝင်သည်- ဖြတ်တောက်ခြင်း → ကြမ်းကြမ်းကြိတ်ခြင်း → အသေးစားကြိတ်ခြင်း → ကြမ်းတမ်းသော ඔප දැමීම (စက်ပိုင်းဆိုင်ရာ දැමීම) → အသေးစား දැමීම (ဓာတုဗေဒ စက်ပိုင်းဆိုင်ရာ දැමීම၊ CMP) → စစ်ဆေးခြင်း။

| ခြေလှမ်း | SiC ဝေဖာ လုပ်ငန်းစဉ် | ရိုးရာ တစ်ပိုင်းလျှပ်ကူးပစ္စည်း တစ်ပုံသဏ္ဌာန် ပုံဆောင်ခဲ ပစ္စည်း စီမံဆောင်ရွက်ခြင်း |

| ဖြတ်တောက်ခြင်း | SiC အချောင်းများကို ပါးလွှာသော ဝေဖာများအဖြစ် လှီးဖြတ်ရန် multi-wire sawing နည်းပညာကို အသုံးပြုသည် | ပုံမှန်အားဖြင့် အတွင်းအချင်း သို့မဟုတ် အပြင်အချင်း ဓားသွားဖြတ်တောက်ခြင်း နည်းစနစ်များကို အသုံးပြုသည် |

| ကြိတ်ခြင်း | ဖြတ်တောက်ခြင်းကြောင့် ဖြစ်ပေါ်လာသော လွှစက်အမှတ်အသားများနှင့် ပျက်စီးမှုအလွှာများကို ဖယ်ရှားရန်အတွက် ကြမ်းတမ်းသောနှင့် အသေးစားကြိတ်ခွဲခြင်းအဖြစ် ခွဲခြားထားသည် | ကြိတ်ခွဲနည်းများ ကွဲပြားနိုင်သော်လည်း ရည်ရွယ်ချက်မှာ အတူတူပင်ဖြစ်သည် |

| ඔප දැමීම | စက်ပိုင်းဆိုင်ရာနှင့် ဓာတုဗေဒဆိုင်ရာ စက်ပိုင်းဆိုင်ရာ ඔප දැමීම (CMP) ကို အသုံးပြု၍ ကြမ်းတမ်းပြီး အလွန်တိကျသော ඔප දැමීම ပါဝင်သည် | ပုံမှန်အားဖြင့် ဓာတုဗေဒဆိုင်ရာ စက်ပိုင်းဆိုင်ရာ ඔප දැමීම (CMP) ပါဝင်သော်လည်း၊ သီးခြားအဆင့်များ ကွဲပြားနိုင်သည် |

SiC တစ်ပုံစံတည်း ပုံဆောင်ခဲများ ဖြတ်တောက်ခြင်း

လုပ်ငန်းစဉ်တွင်SiC တစ်ပိုင်းပုံဆောင်ခဲများ၊ ဖြတ်တောက်ခြင်းသည် ပထမဆုံးနှင့် အလွန်အရေးကြီးသော ခြေလှမ်းတစ်ခုဖြစ်သည်။ ဖြတ်တောက်ခြင်းလုပ်ငန်းစဉ်မှ ဖြစ်ပေါ်လာသော wafer ၏ bow၊ warp နှင့် total thickness variation (TTV) တို့သည် နောက်ဆက်တွဲ grinding နှင့် polishing လုပ်ငန်းများ၏ အရည်အသွေးနှင့် ထိရောက်မှုကို ဆုံးဖြတ်ပေးသည်။

ဖြတ်တောက်သည့်ကိရိယာများကို ပုံသဏ္ဍာန်အလိုက် စိန်အတွင်းအချင်း (ID) လွှများ၊ အပြင်ဘက်အချင်း (OD) လွှများ၊ band saws များနှင့် ဝါယာကြိုးလွှများအဖြစ် အမျိုးအစားခွဲခြားနိုင်သည်။ ဝါယာကြိုးလွှများကို ၎င်းတို့၏ ရွေ့လျားမှုအမျိုးအစားအလိုက် reciprocating နှင့် loop (endless) ဝါယာကြိုးစနစ်များအဖြစ် အမျိုးအစားခွဲခြားနိုင်သည်။ ပွတ်တိုက်ခြင်း၏ ဖြတ်တောက်မှုယန္တရားအပေါ်အခြေခံ၍ ဝါယာကြိုးလွှ လှီးဖြတ်ခြင်းနည်းစနစ်များကို အမျိုးအစားနှစ်မျိုးခွဲခြားနိုင်သည်- free abrasive wire sawing နှင့် fixed abrasive diamond wire sawing။

၁.၁ ရိုးရာဖြတ်တောက်နည်းလမ်းများ

အပြင်ဘက်အချင်း (OD) လွှများ၏ ဖြတ်တောက်မှုအနက်ကို ဓားသွား၏ အချင်းဖြင့် ကန့်သတ်ထားသည်။ ဖြတ်တောက်ခြင်းလုပ်ငန်းစဉ်အတွင်း ဓားသွားသည် တုန်ခါမှုနှင့် သွေဖည်မှုဖြစ်လွယ်ပြီး ဆူညံသံအဆင့်မြင့်မားခြင်းနှင့် မာကျောမှုညံ့ဖျင်းခြင်းတို့ကို ဖြစ်ပေါ်စေသည်။ အတွင်းအချင်း (ID) လွှများသည် ဓားသွား၏ အတွင်းပိုင်းအဝန်းတွင် စိန်ပွတ်တိုက်ပစ္စည်းများကို ဖြတ်တောက်သည့်အနားအဖြစ် အသုံးပြုသည်။ ဤဓားသွားများသည် ၀.၂ မီလီမီတာအထိ ပါးလွှာနိုင်သည်။ လှီးဖြတ်နေစဉ်အတွင်း ID ဓားသွားသည် မြန်နှုန်းမြင့်ဖြင့် လည်ပတ်ပြီး ဖြတ်တောက်မည့်ပစ္စည်းသည် ဓားသွား၏အလယ်ဗဟိုနှင့် ရေဒီယယ်အလိုက် ရွေ့လျားကာ ဤဆွေမျိုးရွေ့လျားမှုမှတစ်ဆင့် လှီးဖြတ်ခြင်းကို ရရှိစေပါသည်။

စိန်ကွင်းလွှများသည် မကြာခဏရပ်တန့်ခြင်းနှင့် ပြောင်းပြန်လှန်ခြင်းများ လိုအပ်ပြီး ဖြတ်တောက်မှုအမြန်နှုန်းသည် အလွန်နိမ့်သည် - ပုံမှန်အားဖြင့် 2 m/s ထက် မပိုပါ။ ၎င်းတို့သည် သိသာထင်ရှားသော စက်ပိုင်းဆိုင်ရာ ယိုယွင်းမှုနှင့် ပြုပြင်ထိန်းသိမ်းမှု ကုန်ကျစရိတ်များခြင်းကိုလည်း ခံစားရသည်။ လွှဓား၏ အကျယ်ကြောင့် ဖြတ်တောက်သည့်အချင်းဝက်သည် အလွန်သေးငယ်၍မရပါ၊ ထို့အပြင် အချပ်များစွာ ဖြတ်တောက်ခြင်းလည်း မဖြစ်နိုင်ပါ။ ဤရိုးရာလွှကိရိယာများသည် အောက်ခြေ၏ မာကျောမှုကြောင့် ကန့်သတ်ထားပြီး ကွေးညွှတ်မှုများကို မပြုလုပ်နိုင်ပါ သို့မဟုတ် လှည့်ပတ်သည့်အချင်းဝက် ကန့်သတ်ချက်များရှိသည်။ ၎င်းတို့သည် ဖြောင့်တန်းသော ဖြတ်တောက်မှုများကိုသာ လုပ်ဆောင်နိုင်ပြီး ကျယ်ပြန့်သော ကွေ့များကို ထုတ်လုပ်နိုင်ပြီး အထွက်နှုန်းနည်းပါးသောကြောင့် ဖြတ်တောက်ရန် မသင့်တော်ပါ။SiC ပုံဆောင်ခဲများ.

၁.၂ ပွတ်တိုက်နိုင်သော ဝါယာကြိုးလွှစက် ဝါယာကြိုးများစွာ ဖြတ်တောက်ခြင်း

free abrasive wire saw slicing နည်းပညာသည် အရည်များကို kerf ထဲသို့ သယ်ဆောင်ရန် ဝါယာကြိုး၏ လျင်မြန်စွာ ရွေ့လျားမှုကို အသုံးပြုပြီး ပစ္စည်းများကို ဖယ်ရှားနိုင်စေပါသည်။ ၎င်းသည် အဓိကအားဖြင့် အပြန်အလှန်ဖွဲ့စည်းမှုကို အသုံးပြုပြီး လက်ရှိတွင် single-crystal silicon ၏ multi-wafer ဖြတ်တောက်မှုအတွက် ရင့်ကျက်ပြီး ကျယ်ကျယ်ပြန့်ပြန့် အသုံးပြုသည့် နည်းလမ်းတစ်ခုဖြစ်သည်။ သို့သော် SiC ဖြတ်တောက်ခြင်းတွင် ၎င်း၏အသုံးချမှုကို ကျယ်ကျယ်ပြန့်ပြန့် လေ့လာထားခြင်း မရှိပါ။

အခမဲ့ abrasive ဝါယာကြိုးလွှများသည် 300 μm အောက် အထူရှိသော ဝေဖာများကို စီမံဆောင်ရွက်နိုင်သည်။ ၎င်းတို့သည် kerf ဆုံးရှုံးမှုနည်းပါးပြီး အက်ကွဲခြင်း ရှားပါးပြီး မျက်နှာပြင်အရည်အသွေး နှိုင်းယှဉ်ကောင်းမွန်သော ရလဒ်ကို ရရှိစေပါသည်။ သို့သော်၊ abrasive များ၏ လှိမ့်ခြင်းနှင့် အပေါက်ဖောက်ခြင်းအပေါ် အခြေခံသည့် ပစ္စည်းဖယ်ရှားရေးယန္တရားကြောင့် ဝေဖာမျက်နှာပြင်သည် သိသာထင်ရှားသော ကျန်ရှိနေသောဖိအား၊ အက်ကွဲကြောင်းငယ်များနှင့် ပိုမိုနက်ရှိုင်းသော ပျက်စီးမှုအလွှာများ ဖြစ်ပေါ်လာတတ်သည်။ ၎င်းသည် ဝေဖာလိမ်ခြင်းကို ဖြစ်ပေါ်စေပြီး မျက်နှာပြင်ပရိုဖိုင်တိကျမှုကို ထိန်းချုပ်ရန် ခက်ခဲစေပြီး နောက်ဆက်တွဲ စီမံဆောင်ရွက်သည့်အဆင့်များတွင် ဝန်ထုပ်ဝန်ပိုးကို တိုးစေသည်။

ဖြတ်တောက်မှုစွမ်းဆောင်ရည်ကို အရည်ပျော်များက များစွာလွှမ်းမိုးထားသည်။ ပွတ်တိုက်ပစ္စည်းများ၏ ထက်မြက်မှုနှင့် အရည်ပျော်၏ ပြင်းအားကို ထိန်းသိမ်းရန် လိုအပ်ပါသည်။ အရည်ပျော်ကုသမှုနှင့် ပြန်လည်အသုံးပြုခြင်းတို့သည် ကုန်ကျစရိတ်များသည်။ အရွယ်အစားကြီးမားသော အချောင်းများကို ဖြတ်တောက်သောအခါ၊ ပွတ်တိုက်ပစ္စည်းများသည် နက်ရှိုင်းပြီး ရှည်လျားသော မျဉ်းကြောင်းများကို ထိုးဖောက်ရန် ခက်ခဲသည်။ ပွတ်တိုက်အမှုန်အရွယ်အစား တူညီပါက၊ မျဉ်းကြောင်းဆုံးရှုံးမှုသည် တည်ငြိမ်သော ပွတ်တိုက်ဝါယာကြိုးလွှများထက် ပိုများသည်။

၁.၃ ပုံသေ ပွတ်တိုက်နိုင်သော စိန်ဝါယာကြိုး လွှစက် ဝါယာကြိုးများစွာ ဖြတ်တောက်ခြင်း

ပုံသေပွတ်တိုက်နိုင်သော စိန်ဝါယာကြိုးလွှများကို စိန်အမှုန်အမွှားများကို သံမဏိဝါယာကြိုးအလွှာပေါ်တွင် ထည့်သွင်းခြင်းဖြင့် electroplating၊ sintering သို့မဟုတ် resin bonding နည်းလမ်းများမှတစ်ဆင့် ပြုလုပ်လေ့ရှိသည်။ Electroplated စိန်ဝါယာကြိုးလွှများသည် ကျဉ်းမြောင်းသော kerfs၊ ပိုမိုကောင်းမွန်သော လှီးဖြတ်အရည်အသွေး၊ မြင့်မားသောစွမ်းဆောင်ရည်၊ ညစ်ညမ်းမှုနည်းပါးခြင်းနှင့် မာကျောမှုမြင့်မားသောပစ္စည်းများကို ဖြတ်တောက်နိုင်စွမ်းကဲ့သို့သော အားသာချက်များကို ပေးစွမ်းသည်။

အပြန်အလှန်လျှပ်စစ်ဓာတ်အားပေးထားသော စိန်ဝါယာကြိုးလွှသည် SiC ဖြတ်တောက်ရန်အတွက် လက်ရှိတွင် အသုံးအများဆုံးနည်းလမ်းဖြစ်သည်။ ပုံ ၁ (ဤနေရာတွင်ပြမထားပါ) သည် ဤနည်းပညာကို အသုံးပြု၍ ဖြတ်တောက်ထားသော SiC ဝေဖာများ၏ မျက်နှာပြင်ပြားချပ်မှုကို သရုပ်ဖော်ထားသည်။ ဖြတ်တောက်မှုတိုးတက်လာသည်နှင့်အမျှ ဝေဖာလိမ်ကောက်မှုတိုးလာသည်။ ၎င်းမှာ ဝါယာကြိုးသည် အောက်သို့ရွေ့လျားလာသည်နှင့်အမျှ ဝါယာကြိုးနှင့် ပစ္စည်းကြားရှိ ထိတွေ့ဧရိယာတိုးလာပြီး ခုခံမှုနှင့် ဝါယာကြိုးတုန်ခါမှုကို တိုးမြင့်စေသောကြောင့်ဖြစ်သည်။ ဝါယာကြိုးသည် ဝေဖာ၏ အများဆုံးအချင်းသို့ရောက်ရှိသောအခါ တုန်ခါမှုသည် အမြင့်ဆုံးတွင်ရှိနေပြီး အများဆုံးလိမ်ကောက်မှုကို ဖြစ်ပေါ်စေသည်။

ဖြတ်တောက်ခြင်း၏ နောက်ပိုင်းအဆင့်များတွင် ဝါယာကြိုးသည် အရှိန်မြှင့်ခြင်း၊ တည်ငြိမ်သောအမြန်နှုန်းရွေ့လျားခြင်း၊ နှေးကွေးခြင်း၊ ရပ်တန့်ခြင်းနှင့် ပြောင်းပြန်ဖြစ်ခြင်းအပြင် အအေးပေးအရည်ဖြင့် အညစ်အကြေးများကို ဖယ်ရှားရာတွင် အခက်အခဲများကြောင့် wafer ၏ မျက်နှာပြင်အရည်အသွေး ယိုယွင်းလာသည်။ ဝါယာကြိုးပြောင်းပြန်ဖြစ်ခြင်းနှင့် မြန်နှုန်းအတက်အကျများအပြင် ဝါယာကြိုးပေါ်ရှိ စိန်အမှုန်အမွှားကြီးများသည် မျက်နှာပြင်ခြစ်ရာများ၏ အဓိကအကြောင်းရင်းများဖြစ်သည်။

၁.၄ အအေးခွဲထုတ်ခြင်းနည်းပညာ

SiC တစ်ပုံဆောင်ခဲများကို အအေးခံခွဲထုတ်ခြင်းသည် တတိယမျိုးဆက် တစ်ပိုင်းလျှပ်ကူးပစ္စည်း လုပ်ငန်းစဉ်တွင် ဆန်းသစ်သော လုပ်ငန်းစဉ်တစ်ခုဖြစ်သည်။ မကြာသေးမီနှစ်များအတွင်း၊ ၎င်းသည် ထွက်နှုန်းတိုးတက်စေပြီး ပစ္စည်းဆုံးရှုံးမှုကို လျှော့ချရာတွင် ထင်ရှားသော အားသာချက်များကြောင့် သိသာထင်ရှားသော အာရုံစိုက်မှုကို ရရှိခဲ့သည်။ နည်းပညာကို ရှုထောင့်သုံးမျိုးမှ ခွဲခြမ်းစိတ်ဖြာနိုင်သည်- အလုပ်လုပ်ပုံနိယာမ၊ လုပ်ငန်းစဉ်စီးဆင်းမှုနှင့် အဓိကအားသာချက်များ။

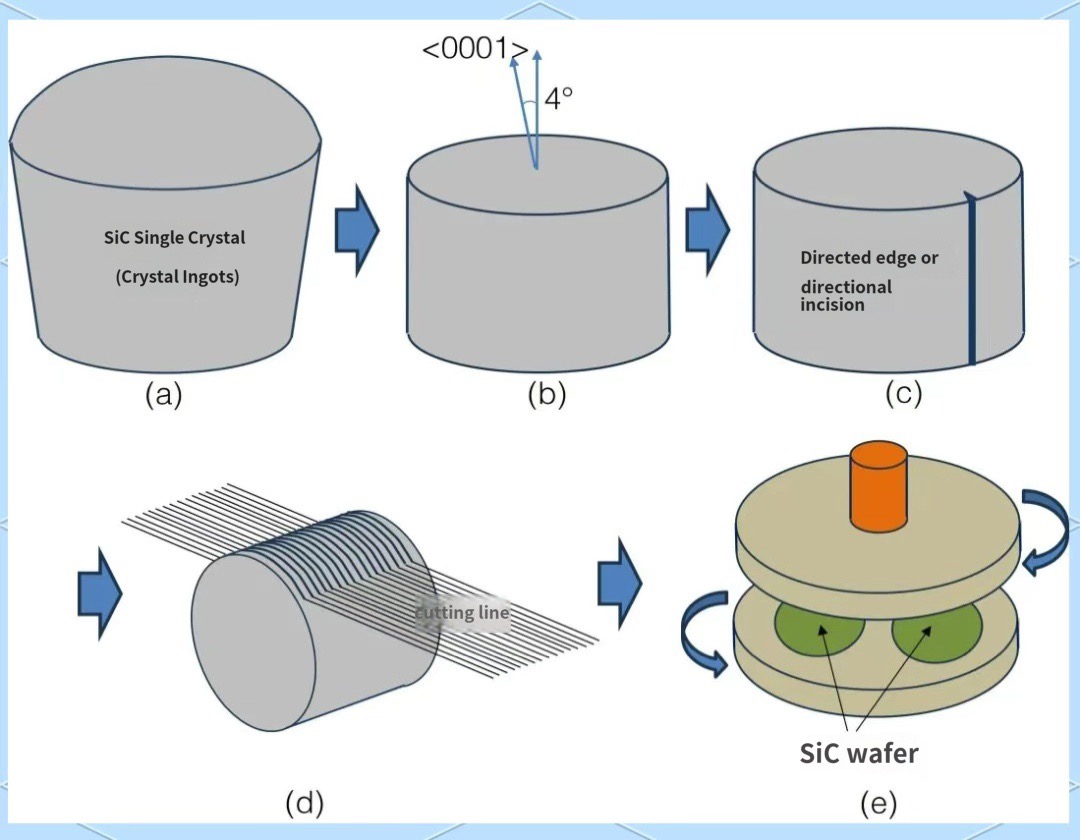

ပုံဆောင်ခဲ ဦးတည်ချက် ဆုံးဖြတ်ခြင်းနှင့် အပြင်ဘက်အချင်း ကြိတ်ခွဲခြင်း- စီမံဆောင်ရွက်ခြင်းမပြုမီ SiC အချောင်း၏ ပုံဆောင်ခဲ ဦးတည်ချက်ကို ဆုံးဖြတ်ရမည်။ ထို့နောက် အချောင်းကို အပြင်ဘက်အချင်း ကြိတ်ခွဲခြင်းမှတစ်ဆင့် ဆလင်ဒါပုံသဏ္ဍာန် (SiC ပါ့ခ်ဟု ခေါ်သည်) အဖြစ် ပုံသွင်းသည်။ ဤအဆင့်သည် နောက်ဆက်တွဲ ဦးတည်ချက်ဖြတ်တောက်ခြင်းနှင့် လှီးဖြတ်ခြင်းအတွက် အုတ်မြစ်ချပေးသည်။

ဝါယာကြိုးများစွာဖြတ်တောက်ခြင်း- ဤနည်းလမ်းသည် ဆလင်ဒါပုံသဏ္ဍာန်အချောင်းကို လှီးဖြတ်ရန်အတွက် ပွတ်တိုက်မှုအမှုန်အမွှားများနှင့် ဝါယာကြိုးများပေါင်းစပ်အသုံးပြုသည်။ သို့သော် ၎င်းသည် သိသာထင်ရှားသော ကွေ့ကောက်မှုဆုံးရှုံးမှုနှင့် မျက်နှာပြင်မညီမညာဖြစ်မှုပြဿနာများကို ကြုံတွေ့ရလေ့ရှိသည်။

လေဆာဖြတ်တောက်ခြင်းနည်းပညာ- ပုံဆောင်ခဲအတွင်း ပြုပြင်ထားသောအလွှာတစ်ခုဖွဲ့စည်းရန် လေဆာကိုအသုံးပြုပြီး ၎င်းမှ ပါးလွှာသောအချပ်များကို ခွဲထုတ်နိုင်သည်။ ဤချဉ်းကပ်မှုသည် ပစ္စည်းဆုံးရှုံးမှုကို လျော့နည်းစေပြီး လုပ်ဆောင်မှုစွမ်းဆောင်ရည်ကို မြှင့်တင်ပေးသောကြောင့် SiC ဝေဖာဖြတ်တောက်ခြင်းအတွက် မျှော်လင့်ချက်ကောင်းသော လမ်းကြောင်းသစ်တစ်ခုဖြစ်လာစေသည်။

ဖြတ်တောက်ခြင်းလုပ်ငန်းစဉ် အကောင်းဆုံးဖြစ်အောင်ပြုလုပ်ခြင်း

ပုံသေ Abrasive Multi-Wire ဖြတ်တောက်ခြင်း- ၎င်းသည် လက်ရှိတွင် SiC ၏ မာကျောမှုမြင့်မားသော ဝိသေသလက္ခဏာများအတွက် အလွန်သင့်လျော်သော အဓိကနည်းပညာဖြစ်သည်။

လျှပ်စစ်အားထုတ်လွှတ်သည့် စက်ဖြင့်ပြုပြင်ခြင်း (EDM) နှင့် အအေးခွဲထုတ်ခြင်းနည်းပညာ- ဤနည်းလမ်းများသည် သီးခြားလိုအပ်ချက်များနှင့် ကိုက်ညီသော ကွဲပြားသောဖြေရှင်းချက်များကို ပေးပါသည်။

ඔප දැමීම လုပ်ငန်းစဉ်- ပစ္စည်းဖယ်ရှားမှုနှုန်းနှင့် မျက်နှာပြင်ပျက်စီးမှုကို ဟန်ချက်ညီစေရန် အရေးကြီးပါသည်။ မျက်နှာပြင်တသမတ်တည်းဖြစ်မှုကို မြှင့်တင်ရန်အတွက် ဓာတုစက်ပိုင်းဆိုင်ရာ දැමීම (CMP) ကို အသုံးပြုပါသည်။

အချိန်နှင့်တပြေးညီ စောင့်ကြည့်ခြင်း- မျက်နှာပြင်ကြမ်းတမ်းမှုကို အချိန်နှင့်တပြေးညီ စောင့်ကြည့်ရန်အတွက် အွန်လိုင်းစစ်ဆေးရေးနည်းပညာများကို မိတ်ဆက်ထားပါသည်။

လေဆာ လှီးဖြတ်ခြင်း- ဤနည်းပညာသည် ကာဗာဆုံးရှုံးမှုကို လျော့နည်းစေပြီး လုပ်ငန်းစဉ်စက်ဝန်းများကို တိုတောင်းစေသော်လည်း အပူဒဏ်သင့်ဇုန်သည် စိန်ခေါ်မှုတစ်ရပ်အဖြစ် ရှိနေဆဲဖြစ်သည်။

Hybrid Processing Technologies: စက်ပိုင်းဆိုင်ရာနှင့် ဓာတုဗေဒဆိုင်ရာနည်းလမ်းများကို ပေါင်းစပ်ခြင်းသည် စီမံဆောင်ရွက်မှုစွမ်းဆောင်ရည်ကို မြှင့်တင်ပေးသည်။

ဤနည်းပညာသည် စက်မှုလုပ်ငန်းသုံး အသုံးချမှုကို အောင်မြင်စွာ လုပ်ဆောင်နိုင်ခဲ့ပြီဖြစ်သည်။ ဥပမာအားဖြင့် Infineon သည် SILTECTRA ကို ဝယ်ယူခဲ့ပြီး ယခုအခါ ၈ လက်မ ဝေဖာများ အစုလိုက်အပြုံလိုက် ထုတ်လုပ်မှုကို ပံ့ပိုးပေးသည့် အဓိက မူပိုင်ခွင့်များကို ပိုင်ဆိုင်ထားသည်။ တရုတ်နိုင်ငံတွင် Delong Laser ကဲ့သို့သော ကုမ္ပဏီများသည် ၆ လက်မ ဝေဖာ လုပ်ဆောင်မှုအတွက် ingot တစ်ခုလျှင် ဝေဖာ ၃၀ ၏ အထွက်စွမ်းဆောင်ရည်ကို ရရှိခဲ့ပြီး၊ ရိုးရာနည်းလမ်းများထက် ၄၀% တိုးတက်မှုကို ကိုယ်စားပြုသည်။

ပြည်တွင်းပစ္စည်းကိရိယာထုတ်လုပ်မှု အရှိန်အဟုန်မြင့်လာသည်နှင့်အမျှ ဤနည်းပညာသည် SiC အောက်ခံပြုပြင်ခြင်းအတွက် အဓိကဖြေရှင်းချက်ဖြစ်လာရန် မျှော်လင့်ရသည်။ တစ်ပိုင်းလျှပ်ကူးပစ္စည်းများ၏ အချင်းတိုးလာသည်နှင့်အမျှ ရိုးရာဖြတ်တောက်ခြင်းနည်းလမ်းများသည် ခေတ်မမီတော့ပါ။ လက်ရှိရွေးချယ်စရာများထဲတွင် အပြန်အလှန်စိန်ဝါယာလွှနည်းပညာသည် အလားအလာအရှိဆုံးအသုံးချမှုအလားအလာများကို ပြသထားသည်။ ပေါ်ထွက်လာသောနည်းပညာတစ်ခုအနေဖြင့် လေဆာဖြတ်တောက်ခြင်းသည် သိသာထင်ရှားသောအားသာချက်များကို ပေးစွမ်းပြီး အနာဂတ်တွင် အဓိကဖြတ်တောက်ခြင်းနည်းလမ်းဖြစ်လာရန် မျှော်လင့်ရသည်။

၂။SiC တစ်ပိုင်းပုံဆောင်ခဲ ကြိတ်ခွဲခြင်း

တတိယမျိုးဆက် တစ်ပိုင်းလျှပ်ကူးပစ္စည်းများ၏ ကိုယ်စားလှယ်တစ်ဦးအနေဖြင့် ဆီလီကွန်ကာဗိုက် (SiC) သည် ၎င်း၏ ကျယ်ပြန့်သော bandgap၊ မြင့်မားသော ပြိုကွဲလျှပ်စစ်စက်ကွင်း၊ မြင့်မားသော saturation electron drift velocity နှင့် အလွန်ကောင်းမွန်သော အပူစီးကူးမှုကြောင့် သိသာထင်ရှားသော အားသာချက်များကို ပေးစွမ်းသည်။ ဤဂုဏ်သတ္တိများသည် SiC ကို မြင့်မားသောဗို့အားအသုံးချမှုများ (ဥပမာ၊ 1200V ပတ်ဝန်းကျင်) တွင် အထူးအကျိုးရှိစေသည်။ SiC အောက်ခံများအတွက် လုပ်ဆောင်ခြင်းနည်းပညာသည် စက်ပစ္စည်းထုတ်လုပ်ခြင်း၏ အခြေခံအစိတ်အပိုင်းတစ်ခုဖြစ်သည်။ အောက်ခံ၏ မျက်နှာပြင်အရည်အသွေးနှင့် တိကျမှုသည် epitaxial layer ၏ အရည်အသွေးနှင့် နောက်ဆုံးစက်ပစ္စည်း၏ စွမ်းဆောင်ရည်ကို တိုက်ရိုက်အကျိုးသက်ရောက်စေသည်။

ကြိတ်ခွဲခြင်းလုပ်ငန်းစဉ်၏ အဓိကရည်ရွယ်ချက်မှာ လှီးဖြတ်စဉ်အတွင်း ဖြစ်ပေါ်လာသော မျက်နှာပြင်လွှအမှတ်အသားများနှင့် ပျက်စီးမှုအလွှာများကို ဖယ်ရှားရန်နှင့် ဖြတ်တောက်ခြင်းလုပ်ငန်းစဉ်ကြောင့် ဖြစ်ပေါ်လာသော ပုံပျက်ခြင်းကို ပြုပြင်ရန်ဖြစ်သည်။ SiC ၏ အလွန်မာကျောမှုမြင့်မားသောကြောင့် ကြိတ်ခွဲခြင်းတွင် ဘိုရွန်ကာဗိုက် သို့မဟုတ် စိန်ကဲ့သို့သော မာကျောသောပွတ်တိုက်ပစ္စည်းများကို အသုံးပြုရန် လိုအပ်ပါသည်။ ရိုးရာကြိတ်ခွဲခြင်းကို ယေဘုယျအားဖြင့် ကြမ်းကြမ်းကြိတ်ခွဲခြင်းနှင့် အသေးစားကြိတ်ခွဲခြင်းအဖြစ် ခွဲခြားထားသည်။

၂.၁ ကြမ်းတမ်းသောနှင့် အသေးစားကြိတ်ခွဲခြင်း

ကြိတ်ခွဲခြင်းကို ပွတ်တိုက်မှုအမှုန်အရွယ်အစားပေါ် မူတည်၍ အမျိုးအစားခွဲခြားနိုင်သည်-

ကြမ်းတမ်းစွာ ကြိတ်ခွဲခြင်း- လှီးဖြတ်စဉ် ဖြစ်ပေါ်လာသော လွှစက်ရာများနှင့် ပျက်စီးမှုအလွှာများကို ဖယ်ရှားရန် အဓိကအားဖြင့် ပိုကြီးသော ပွတ်တိုက်ပစ္စည်းများကို အသုံးပြုပြီး လုပ်ငန်းစဉ်စွမ်းဆောင်ရည်ကို မြှင့်တင်ပေးသည်။

အနုစိတ်ကြိတ်ခွဲခြင်း- ကြမ်းကြမ်းကြိတ်ခွဲခြင်းကြောင့် ကျန်ရှိနေသော ပျက်စီးမှုအလွှာကို ဖယ်ရှားရန်၊ မျက်နှာပြင်ကြမ်းတမ်းမှုကို လျှော့ချရန်နှင့် မျက်နှာပြင်အရည်အသွေးကို မြှင့်တင်ရန်အတွက် ပိုမိုပါးလွှာသော ပွန်းစားပစ္စည်းများကို အသုံးပြုသည်။

ပြည်တွင်း SiC အောက်ခံထုတ်လုပ်သူများစွာသည် ကြီးမားသောထုတ်လုပ်မှုလုပ်ငန်းစဉ်များကို အသုံးပြုကြသည်။ အသုံးများသောနည်းလမ်းတစ်ခုမှာ သံမဏိပြားနှင့် monocrystalline စိန်အရည်ကို အသုံးပြု၍ နှစ်ဖက်ကြိတ်ခွဲခြင်းပါဝင်သည်။ ဤလုပ်ငန်းစဉ်တွင် ဝါယာကြိုးလွှစက်ဖြင့် ဖြတ်တောက်ခြင်းကြောင့် ကျန်ရှိနေသော ပျက်စီးမှုအလွှာကို ထိရောက်စွာဖယ်ရှားပေးပြီး၊ wafer ပုံသဏ္ဍာန်ကို ပြုပြင်ပေးကာ TTV (စုစုပေါင်းအထူပြောင်းလဲမှု)၊ Bow နှင့် Warp တို့ကို လျှော့ချပေးသည်။ ပစ္စည်းဖယ်ရှားမှုနှုန်းသည် တည်ငြိမ်ပြီး ပုံမှန်အားဖြင့် 0.8–1.2 μm/min အထိ ရောက်ရှိသည်။ သို့သော်၊ ရလဒ် wafer မျက်နှာပြင်သည် ကြမ်းတမ်းမှုမြင့်မားပြီး ပုံမှန်အားဖြင့် 50 nm ဝန်းကျင်ရှိကာ ඔප දැමීමීමဖြစ်သည်။ ၎င်းသည် နောက်ဆက်တွဲ ඔප දැමීම အဆင့်များတွင် ပိုမိုမြင့်မားသော လိုအပ်ချက်များကို ဖြစ်ပေါ်စေပါသည်။

၂.၂ တစ်ဖက်တည်းကြိတ်ခြင်း

တစ်ဖက်သတ်ကြိတ်ခွဲခြင်းသည် ဝေဖာ၏ တစ်ဖက်ကိုသာ တစ်ကြိမ်လျှင် ကြိတ်ခွဲသည်။ ဤလုပ်ငန်းစဉ်အတွင်း ဝေဖာကို သံမဏိပြားပေါ်တွင် ဖယောင်းဖြင့် တပ်ဆင်ထားသည်။ ဖိအားပေးသောအခါ၊ အောက်ခံမျက်နှာပြင်သည် အနည်းငယ်ပုံပျက်သွားပြီး အပေါ်မျက်နှာပြင်သည် ပြားသွားသည်။ ကြိတ်ခွဲပြီးနောက် အောက်မျက်နှာပြင်သည် ညီညာသွားသည်။ ဖိအားဖယ်ရှားလိုက်သောအခါ အပေါ်မျက်နှာပြင်သည် မူလပုံသဏ္ဍာန်သို့ ပြန်လည်ရောက်ရှိသွားပြီး ၎င်းသည် ကြိတ်ခွဲပြီးသား အောက်မျက်နှာပြင်ကိုလည်း သက်ရောက်မှုရှိပြီး နှစ်ဖက်စလုံးသည် ကွေးညွှတ်ပြီး ပြားချပ်ချပ်ဖြစ်ခြင်းကို ဖြစ်စေသည်။

ထို့အပြင်၊ ကြိတ်ခွဲပြားသည် အချိန်တိုအတွင်း ခွက်ဝင်သွားနိုင်ပြီး ဝေဖာသည် ခုံးထွက်စေပါသည်။ ပြား၏ ပြားချပ်မှုကို ထိန်းသိမ်းရန်အတွက် မကြာခဏ ဖုံးအုပ်ပေးရန် လိုအပ်သည်။ ထိရောက်မှုနည်းပါးခြင်းနှင့် ဝေဖာပြားချပ်မှု ညံ့ဖျင်းခြင်းကြောင့် တစ်ဖက်တည်းကြိတ်ခွဲခြင်းသည် အစုလိုက်အပြုံလိုက်ထုတ်လုပ်မှုအတွက် မသင့်တော်ပါ။

ပုံမှန်အားဖြင့် #8000 ကြိတ်ဘီးများကို ကြိတ်ခွဲရန်အတွက် အသုံးပြုကြသည်။ ဂျပန်နိုင်ငံတွင် ဤလုပ်ငန်းစဉ်သည် အတော်လေးရင့်ကျက်ပြီး #30000 ပွတ်တိုက်ဘီးများကိုပင် အသုံးပြုသည်။ ၎င်းသည် စီမံဆောင်ရွက်ထားသော ဝေဖာများ၏ မျက်နှာပြင်ကြမ်းတမ်းမှုကို 2 nm အောက်သို့ ရောက်ရှိစေပြီး အပိုလုပ်ငန်းစဉ်မပါဘဲ ဝေဖာများကို နောက်ဆုံး CMP (ဓာတုစက်ပိုင်းဆိုင်ရာ ပွတ်တိုက်ခြင်း) အတွက် အသင့်ဖြစ်စေသည်။

၂.၃ တစ်ဖက်တည်းဖြင့် ပါးလွှာစေသော နည်းပညာ

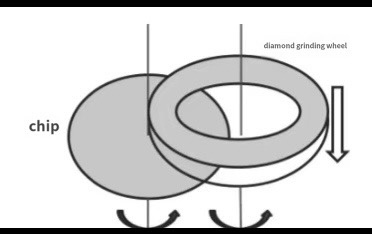

စိန်တစ်ဖက်တည်းဖြင့် ပါးလွှာစေသည့် နည်းပညာသည် တစ်ဖက်တည်းဖြင့် ကြိတ်ခွဲခြင်း၏ နည်းလမ်းအသစ်တစ်ခုဖြစ်သည်။ ပုံ ၅ (ဤနေရာတွင် မပြထားပါ) တွင် ပြသထားသည့်အတိုင်း၊ ဤလုပ်ငန်းစဉ်သည် စိန်ဖြင့် ချည်နှောင်ထားသော ကြိတ်ခွဲပြားကို အသုံးပြုသည်။ ဝေဖာကို vacuum adsorption မှတစ်ဆင့် တပ်ဆင်ထားပြီး ဝေဖာနှင့် စိန်ကြိတ်ဘီး နှစ်ခုစလုံးသည် တစ်ပြိုင်နက်တည်း လည်ပတ်နေသည်။ ကြိတ်ဘီးသည် ဝေဖာကို ပစ်မှတ်အထူအထိ ပါးလွှာစေရန် တဖြည်းဖြည်း အောက်သို့ ရွေ့လျားသည်။ တစ်ဖက်ပြီးသွားပြီးနောက် ဝေဖာကို လှန်ပြီး အခြားတစ်ဖက်ကို စီမံဆောင်ရွက်သည်။

ပါးလွှာပြီးနောက်၊ 100 မီလီမီတာ ဝေဖာသည် အောက်ပါတို့ကို ရရှိနိုင်သည်-

ကွေး < ၅ မိုက်ခရိုမီတာ

TTV < ၂ မိုက်ခရိုမီတာ

မျက်နှာပြင်ကြမ်းတမ်းမှု < 1 nm

ဤ single-wafer လုပ်ဆောင်ခြင်းနည်းလမ်းသည် မြင့်မားသောတည်ငြိမ်မှု၊ အလွန်ကောင်းမွန်သော တသမတ်တည်းရှိမှုနှင့် မြင့်မားသောပစ္စည်းဖယ်ရှားမှုနှုန်းကို ပေးစွမ်းသည်။ ရိုးရာနှစ်ဖက်ကြိတ်ခွဲခြင်းနှင့် နှိုင်းယှဉ်ပါက ဤနည်းပညာသည် ကြိတ်ခွဲမှုစွမ်းဆောင်ရည်ကို 50% ကျော် တိုးတက်စေသည်။

၂.၄ နှစ်ဖက်ကြိတ်ခွဲခြင်း

နှစ်ဖက်ကြိတ်ခွဲခြင်းသည် အပေါ်ပိုင်းကြိတ်ပြားနှင့် အောက်ပိုင်းကြိတ်ပြား နှစ်မျိုးလုံးကို အသုံးပြု၍ အောက်ခံအလွှာ၏ နှစ်ဖက်စလုံးကို တစ်ပြိုင်နက်ကြိတ်ခွဲပေးသောကြောင့် နှစ်ဖက်စလုံးတွင် မျက်နှာပြင်အရည်အသွေး အလွန်ကောင်းမွန်ကြောင်း သေချာစေသည်။

လုပ်ငန်းစဉ်အတွင်း၊ ကြိတ်ခွဲပြားများသည် အလုပ်၏ အမြင့်ဆုံးနေရာများသို့ ဦးစွာဖိအားပေးကာ ပုံပျက်ခြင်းနှင့် ထိုနေရာများတွင် တဖြည်းဖြည်း ပစ္စည်းဖယ်ရှားခြင်းကို ဖြစ်ပေါ်စေပါသည်။ အမြင့်ဆုံးနေရာများ ညီညာသွားသည်နှင့်အမျှ၊ အောက်ခံပေါ်ရှိဖိအားသည် တဖြည်းဖြည်း ပိုမိုညီညာလာပြီး မျက်နှာပြင်တစ်ခုလုံးတွင် တသမတ်တည်း ပုံပျက်ခြင်းကို ဖြစ်ပေါ်စေပါသည်။ ၎င်းသည် အပေါ်နှင့်အောက် မျက်နှာပြင်နှစ်ခုလုံးကို ညီညာစွာကြိတ်ခွဲနိုင်စေပါသည်။ ကြိတ်ခွဲခြင်းပြီးဆုံးပြီး ဖိအားထွက်လာသည်နှင့် အောက်ခံ၏ အစိတ်အပိုင်းတစ်ခုစီသည် ၎င်းခံစားခဲ့ရသော တူညီသောဖိအားကြောင့် ညီညာစွာပြန်လည်ကောင်းမွန်လာပါသည်။ ၎င်းသည် အနည်းဆုံး ကောက်ကွေးခြင်းနှင့် ကောင်းမွန်သော ပြားချပ်ချပ်ဖြစ်ခြင်းကို ဖြစ်ပေါ်စေသည်။

ကြိတ်ခွဲပြီးနောက် ဝေဖာ၏ မျက်နှာပြင်ကြမ်းတမ်းမှုသည် ပွတ်တိုက်မှုအမှုန်အရွယ်အစားပေါ်တွင် မူတည်သည်—အမှုန်ငယ်များသည် ချောမွေ့သောမျက်နှာပြင်များကို ရရှိစေပါသည်။ နှစ်ဖက်ကြိတ်ခွဲခြင်းအတွက် 5 μm ပွတ်တိုက်ပစ္စည်းများကို အသုံးပြုသောအခါ၊ ဝေဖာပြားချပ်မှုနှင့် အထူပြောင်းလဲမှုကို 5 μm အတွင်း ထိန်းချုပ်နိုင်သည်။ Atomic Force Microscopy (AFM) တိုင်းတာမှုများက မျက်နှာပြင်ကြမ်းတမ်းမှု (Rq) 100 nm ခန့်ရှိပြီး၊ 380 nm အနက်အထိ ကြိတ်ခွဲသည့်အပေါက်များနှင့် ပွတ်တိုက်မှုကြောင့် ဖြစ်ပေါ်လာသော မြင်သာသော မျဉ်းဖြောင့်အမှတ်အသားများကို ပြသသည်။

ပိုမိုအဆင့်မြင့်သောနည်းလမ်းတွင် polyurethane foam pads များနှင့် polycrystalline diamond slurry တို့ကို ပေါင်းစပ်အသုံးပြု၍ နှစ်ဖက်ကြိတ်ခွဲခြင်းပါဝင်သည်။ ဤလုပ်ငန်းစဉ်သည် မျက်နှာပြင်ကြမ်းတမ်းမှုအလွန်နည်းသော wafer များကိုထုတ်လုပ်ပေးပြီး Ra < 3 nm ရရှိကာ SiC အောက်ခံများကို ඔප දැමීමීමအတွက် အလွန်အကျိုးရှိပါသည်။

သို့သော် မျက်နှာပြင်ကုတ်ခြစ်ခြင်းသည် မဖြေရှင်းရသေးသောပြဿနာတစ်ခုအဖြစ် ရှိနေဆဲဖြစ်သည်။ ထို့အပြင်၊ ဤလုပ်ငန်းစဉ်တွင်အသုံးပြုသော polycrystalline စိန်ကို ပေါက်ကွဲစေတတ်သောပေါင်းစပ်မှုမှတစ်ဆင့် ထုတ်လုပ်ပြီး နည်းပညာအရစိန်ခေါ်မှုရှိပြီး ပမာဏနည်းပါးကာ အလွန်စျေးကြီးသည်။

SiC တစ်ပုံစံတည်း ပုံဆောင်ခဲများကို ඔප දැමීමခြင်း

ဆီလီကွန်ကာဗိုက် (SiC) ဝေဖာများပေါ်တွင် အရည်အသွေးမြင့် ඔප දැමීම မျက်နှာပြင်ရရှိရန်အတွက် ඔප දැමීමသည် ကြိတ်ခွဲထားသော အပေါက်များနှင့် နာနိုမီတာစကေး မျက်နှာပြင် လှိုင်းတွန့်များကို လုံးဝဖယ်ရှားရမည်။ ရည်မှန်းချက်မှာ ညစ်ညမ်းမှု သို့မဟုတ် ယိုယွင်းပျက်စီးမှုမရှိ၊ မျက်နှာပြင်အောက် ပျက်စီးမှုမရှိ၊ မျက်နှာပြင်ဖိအား အကြွင်းအကျန်မရှိသော ချောမွေ့ပြီး အပြစ်အနာအဆာကင်းသော မျက်နှာပြင်ကို ထုတ်လုပ်ရန်ဖြစ်သည်။

၃.၁ SiC ဝေဖာများ၏ စက်ပိုင်းဆိုင်ရာ ඔප දැමීමနှင့် CMP

SiC single crystal ingot ကြီးထွားပြီးနောက်၊ မျက်နှာပြင်ချို့ယွင်းချက်များက ၎င်းကို epitaxial ကြီးထွားမှုအတွက် တိုက်ရိုက်အသုံးမပြုနိုင်စေပါ။ ထို့ကြောင့်၊ နောက်ထပ်လုပ်ဆောင်ရန် လိုအပ်ပါသည်။ ingot ကို ဦးစွာ rounding မှတစ်ဆင့် standard cylindrical form ဖြစ်အောင်ပုံသွင်းပြီးနောက် wire cutting ကို အသုံးပြု၍ wafers များအဖြစ် လှီးဖြတ်ပြီးနောက် crystallographic orientation verification ဖြင့် လုပ်ဆောင်သည်။ wafer အရည်အသွေးတိုးတက်စေရန်၊ crystal ကြီးထွားမှုချို့ယွင်းချက်များနှင့် ယခင်လုပ်ဆောင်ခြင်းအဆင့်များကြောင့် ဖြစ်ပေါ်လာနိုင်သော မျက်နှာပြင်ပျက်စီးမှုကို ဖြေရှင်းရာတွင် polishing သည် အရေးကြီးသောခြေလှမ်းတစ်ခုဖြစ်သည်။

SiC ပေါ်ရှိ မျက်နှာပြင်ပျက်စီးမှုအလွှာများကို ဖယ်ရှားရန် အဓိကနည်းလမ်းလေးခုရှိသည်-

စက်ပိုင်းဆိုင်ရာ ඔප දැමීම- ရိုးရှင်းသော်လည်း ခြစ်ရာများကျန်ခဲ့သည်။ ကနဦး ඔප දැමීමအတွက် သင့်လျော်သည်။

ဓာတုစက်ပိုင်းဆိုင်ရာ ඔප දැමීම (CMP): ဓာတုထွင်းထုခြင်းမှတစ်ဆင့် ခြစ်ရာများကို ဖယ်ရှားပေးသည်။ တိကျသော ඔප දැමීමအတွက် သင့်လျော်သည်။

ဟိုက်ဒရိုဂျင် ထွင်းထုခြင်း- HTCVD လုပ်ငန်းစဉ်များတွင် အသုံးများသော ရှုပ်ထွေးသော ပစ္စည်းကိရိယာများ လိုအပ်ပါသည်။

ပလာစမာအကူအညီဖြင့် ඔප දැමීම- ရှုပ်ထွေးပြီး ရှားရှားပါးပါးသာ အသုံးပြုသည်။

စက်ပိုင်းဆိုင်ရာသာ ඔප දැමීමသည် ခြစ်ရာများဖြစ်စေတတ်ပြီး ဓာတုဗေဒဆိုင်ရာသာ දැමීමသည် မညီမညာ ထွင်းထုခြင်းများကို ဖြစ်စေနိုင်သည်။ CMP ၏ အားသာချက်နှစ်ခုလုံးကို ပေါင်းစပ်ထားပြီး ထိရောက်ပြီး ကုန်ကျစရိတ်သက်သာသော ဖြေရှင်းချက်ကို ပေးဆောင်သည်။

CMP လုပ်ငန်းလည်ပတ်မှုမူ

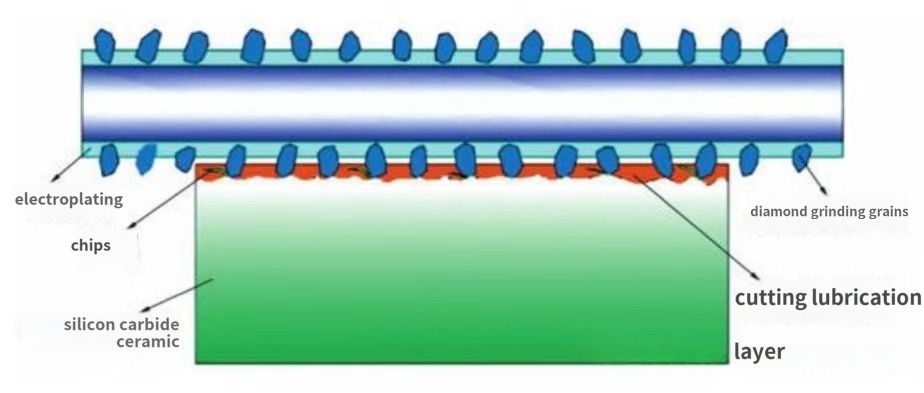

CMP သည် လည်ပတ်နေသော ඔප දැමීමကို သတ်မှတ်ထားသောဖိအားအောက်တွင် wafer ကိုလှည့်ခြင်းဖြင့် အလုပ်လုပ်သည်။ ဤနှိုင်းရရွေ့လျားမှုသည် အရည်ပျော်တွင်ရှိသော နာနိုအရွယ် ඔප දැමීමများမှ စက်ပိုင်းဆိုင်ရာ ပွတ်တိုက်မှုနှင့် ဓာတ်ပြုပစ္စည်းများ၏ ဓာတုလုပ်ဆောင်ချက်တို့နှင့် ပေါင်းစပ်ခြင်းဖြင့် မျက်နှာပြင်ပြားချပ်စေသည်။

အသုံးပြုထားသော အဓိကပစ္စည်းများ-

ඔප දැමීම- ပွတ်တိုက်ပစ္စည်းများနှင့် ဓာတုပစ္စည်းများ ပါဝင်သည်။

ඔප දැමීම: အသုံးပြုနေစဉ်အတွင်း ඔප දැමීම လျော့ပါးသွားပြီး အပေါက်အရွယ်အစားနှင့် දැමීම ထိရောက်မှုကို လျော့ကျစေသည်။ ကြမ်းတမ်းမှုကို ပြန်လည်ရရှိစေရန်အတွက် ပုံမှန် ඔප දැමීම၊ များသောအားဖြင့် စိန်ထည်စက်ကို အသုံးပြု၍ လိမ်းပေးရန် လိုအပ်ပါသည်။

ပုံမှန် CMP လုပ်ငန်းစဉ်

ပွန်းစားခြင်း- 0.5 μm စိန်အရည်

ပစ်မှတ်မျက်နှာပြင်ကြမ်းတမ်းမှု: ~0.7 nm

ဓာတုဗေဒဆိုင်ရာ စက်ပိုင်းဆိုင်ရာ ඔප දැමීම:

ඔප දැමීම- AP-810 တစ်ဖက်တည်း දැමීම

ဖိအား: ၂၀၀ ဂရမ်/စင်တီမီတာ²

ပန်းကန်ပြားအမြန်နှုန်း: 50 rpm

ကြွေထည်ကိုင်ဆောင်သူ၏ မြန်နှုန်း: 38 rpm

အရည်ပျော်ပါဝင်မှု

SiO₂ (၃၀ wt%၊ pH = ၁၀.၁၅)

၀–၇၀ wt% H₂O₂ (၃၀ wt%၊ ဓါတ်ကူပစ္စည်းအဆင့်)

၅ wt% KOH နှင့် ၁ wt% HNO₃ ကို အသုံးပြု၍ pH ကို ၈.၅ သို့ ချိန်ညှိပါ။

အရည်စီးဆင်းမှုနှုန်း: တစ်မိနစ်လျှင် ၃ လီတာ၊ ပြန်လည်လည်ပတ်သည်

ဤလုပ်ငန်းစဉ်သည် SiC wafer အရည်အသွေးကို ထိရောက်စွာ တိုးတက်ကောင်းမွန်စေပြီး downstream လုပ်ငန်းစဉ်များအတွက် လိုအပ်ချက်များနှင့် ကိုက်ညီပါသည်။

စက်ပိုင်းဆိုင်ရာ ඔප දැමීමတွင် နည်းပညာဆိုင်ရာ စိန်ခေါ်မှုများ

SiC သည် bandgap ကျယ်သော semiconductor တစ်ခုဖြစ်သည့်အတွက် အီလက်ထရွန်းနစ်လုပ်ငန်းတွင် အရေးပါသောအခန်းကဏ္ဍမှ ပါဝင်သည်။ အလွန်ကောင်းမွန်သော ရုပ်ပိုင်းဆိုင်ရာနှင့် ဓာတုဗေဒဂုဏ်သတ္တိများဖြင့် SiC single crystals များသည် အပူချိန်မြင့်မားခြင်း၊ ကြိမ်နှုန်းမြင့်မားခြင်း၊ ပါဝါမြင့်မားခြင်းနှင့် ရောင်ခြည်ဒဏ်ခံနိုင်ရည်ရှိခြင်းကဲ့သို့သော အစွန်းရောက်ပတ်ဝန်းကျင်များအတွက် သင့်လျော်ပါသည်။ သို့သော် ၎င်း၏ မာကျောပြီး ကြွပ်ဆတ်သောသဘောသဘာဝသည် ကြိတ်ခွဲခြင်းနှင့် ඔප දැමීමအတွက် အဓိကစိန်ခေါ်မှုများကို ဖြစ်ပေါ်စေသည်။

ကမ္ဘာ့ဦးဆောင်ထုတ်လုပ်သူများသည် ၆ လက်မ ဝေဖာများမှ ၈ လက်မ ဝေဖာများသို့ ကူးပြောင်းလာသည်နှင့်အမျှ အက်ကွဲခြင်းနှင့် လုပ်ဆောင်နေစဉ် ဝေဖာပျက်စီးခြင်းကဲ့သို့သော ပြဿနာများသည် ပိုမိုထင်ရှားလာပြီး ထွက်နှုန်းကို သိသိသာသာ ထိခိုက်စေပါသည်။ ၈ လက်မ SiC အောက်ခံများ၏ နည်းပညာဆိုင်ရာစိန်ခေါ်မှုများကို ဖြေရှင်းခြင်းသည် ယခုအခါ လုပ်ငန်းတိုးတက်မှုအတွက် အဓိကစံနှုန်းတစ်ခုဖြစ်သည်။

၈ လက်မခေတ်တွင် SiC wafer လုပ်ဆောင်ခြင်းသည် စိန်ခေါ်မှုများစွာနှင့် ရင်ဆိုင်ရပါသည်-

အထူးသဖြင့် လျှပ်စစ်ကားအသုံးချမှုများတွင် မြင့်တက်လာသော ဝယ်လိုအားကို ထည့်သွင်းစဉ်းစားပါက — အသုတ်တစ်ခုလျှင် ချစ်ပ်ထုတ်လုပ်မှုကို တိုးမြှင့်ရန်၊ အနားစွန်းဆုံးရှုံးမှုကို လျှော့ချရန်နှင့် ထုတ်လုပ်မှုကုန်ကျစရိတ်များကို လျှော့ချရန်အတွက် Wafer scaling လိုအပ်ပါသည်။

၈ လက်မ SiC တစ်ပုံးပုံဆောင်ခဲများ၏ ကြီးထွားမှု ရင့်ကျက်လာသော်လည်း၊ ကြိတ်ခွဲခြင်းနှင့် ඔප දැමීමကဲ့သို့သော နောက်ကွယ်လုပ်ငန်းစဉ်များသည် ပိတ်ဆို့မှုများနှင့် ရင်ဆိုင်နေရဆဲဖြစ်ပြီး၊ အထွက်နှုန်းနည်းပါးခြင်း (၄၀-၅၀%) သာ ဖြစ်ပေါ်စေပါသည်။

ပိုကြီးသော ဝေဖာများသည် ပိုမိုရှုပ်ထွေးသော ဖိအားဖြန့်ဖြူးမှုကို ကြုံတွေ့ရပြီး ඔප දැමීමနှင့် အထွက်နှုန်း တသမတ်တည်းဖြစ်မှုကို စီမံခန့်ခွဲရန် အခက်အခဲကို တိုးမြင့်စေသည်။

၈ လက်မ ဝေဖာများ၏ အထူသည် ၆ လက်မ ဝေဖာများထက် နီးကပ်လာသော်လည်း၊ ဖိစီးမှုနှင့် ကောက်ကွေးမှုကြောင့် ကိုင်တွယ်စဉ်အတွင်း ပျက်စီးမှု ပိုမိုဖြစ်လွယ်ပါသည်။

ဖြတ်တောက်ခြင်းနှင့်ဆက်စပ်သောဖိစီးမှု၊ ကောက်ကွေးမှုနှင့် အက်ကွဲခြင်းကို လျှော့ချရန်အတွက် လေဆာဖြတ်တောက်ခြင်းကို ပိုမိုအသုံးပြုလာကြသည်။ သို့သော်-

ရှည်လျားသော လှိုင်းအလျား လေဆာများသည် အပူဒဏ်ကို ဖြစ်စေသည်။

လှိုင်းတိုလေဆာများသည် လေးလံသောအပျက်အစီးများကို ထုတ်လွှတ်ပြီး ပျက်စီးမှုအလွှာကို ပိုမိုနက်ရှိုင်းစေကာ ඔප දැමීම ရှုပ်ထွေးမှုကို တိုးမြင့်စေသည်။

SiC အတွက် စက်ပိုင်းဆိုင်ရာ ඔප දැමීම လုပ်ငန်းစဉ်

အထွေထွေလုပ်ငန်းစဉ်စီးဆင်းမှုတွင် အောက်ပါတို့ပါဝင်သည်-

ဦးတည်ချက်ဖြတ်တောက်ခြင်း

ကြမ်းတမ်းစွာကြိတ်ခြင်း

အနုစိတ်ကြိတ်ခွဲခြင်း

စက်ပိုင်းဆိုင်ရာ ඔප දැමීම

နောက်ဆုံးအဆင့်အနေဖြင့် ဓာတုဗေဒဆိုင်ရာ စက်ပိုင်းဆိုင်ရာ ඔප දැමීම (CMP)

CMP နည်းလမ်းရွေးချယ်မှု၊ လုပ်ငန်းစဉ်လမ်းကြောင်းဒီဇိုင်းနှင့် ကန့်သတ်ချက်များကို အကောင်းဆုံးဖြစ်အောင်ပြုလုပ်ခြင်းသည် အလွန်အရေးကြီးပါသည်။ တစ်ပိုင်းလျှပ်ကူးပစ္စည်းထုတ်လုပ်မှုတွင် CMP သည် အရည်အသွေးမြင့် epitaxial ကြီးထွားမှုအတွက် မရှိမဖြစ်လိုအပ်သော အလွန်ချောမွေ့သော၊ အပြစ်အနာအဆာကင်းသော နှင့် ပျက်စီးမှုကင်းသော မျက်နှာပြင်များပါရှိသော SiC ဝေဖာများထုတ်လုပ်ရန် ဆုံးဖြတ်သည့်အဆင့်ဖြစ်သည်။

(က) SiC အချောင်းကို crucible မှ ဖယ်ရှားပါ။

(ခ) အပြင်ဘက်အချင်းဝက် ကြိတ်ခွဲခြင်းကို အသုံးပြု၍ ကနဦးပုံသွင်းခြင်းကို လုပ်ဆောင်ပါ။

(ဂ) alignment flats သို့မဟုတ် notches များကို အသုံးပြု၍ crystal orientation ကို ဆုံးဖြတ်ပါ။

(ဃ) ဝါယာကြိုးများစွာပါသော လွှစက်ကို အသုံးပြု၍ အချောင်းကို ပါးလွှာသော ဝေဖာများအဖြစ် လှီးဖြတ်ပါ။

(င) ကြိတ်ခွဲခြင်းနှင့် ඔප දැමීම အဆင့်များမှတစ်ဆင့် မှန်ကဲ့သို့ မျက်နှာပြင်ချောမွေ့မှုကို ရရှိစေပါ။

လုပ်ဆောင်ခြင်းအဆင့်များ ပြီးမြောက်ပြီးနောက်၊ SiC wafer ၏ အပြင်ဘက်အနားသည် မကြာခဏ ထက်မြက်လာတတ်ပြီး ကိုင်တွယ်ခြင်း သို့မဟုတ် အသုံးပြုခြင်းတွင် အက်ကွဲခြင်းအန္တရာယ်ကို တိုးမြင့်စေသည်။ ထိုကဲ့သို့သော ပျက်စီးလွယ်မှုကို ရှောင်ရှားရန်အတွက် အနားသတ်များ ကြိတ်ခွဲရန် လိုအပ်ပါသည်။

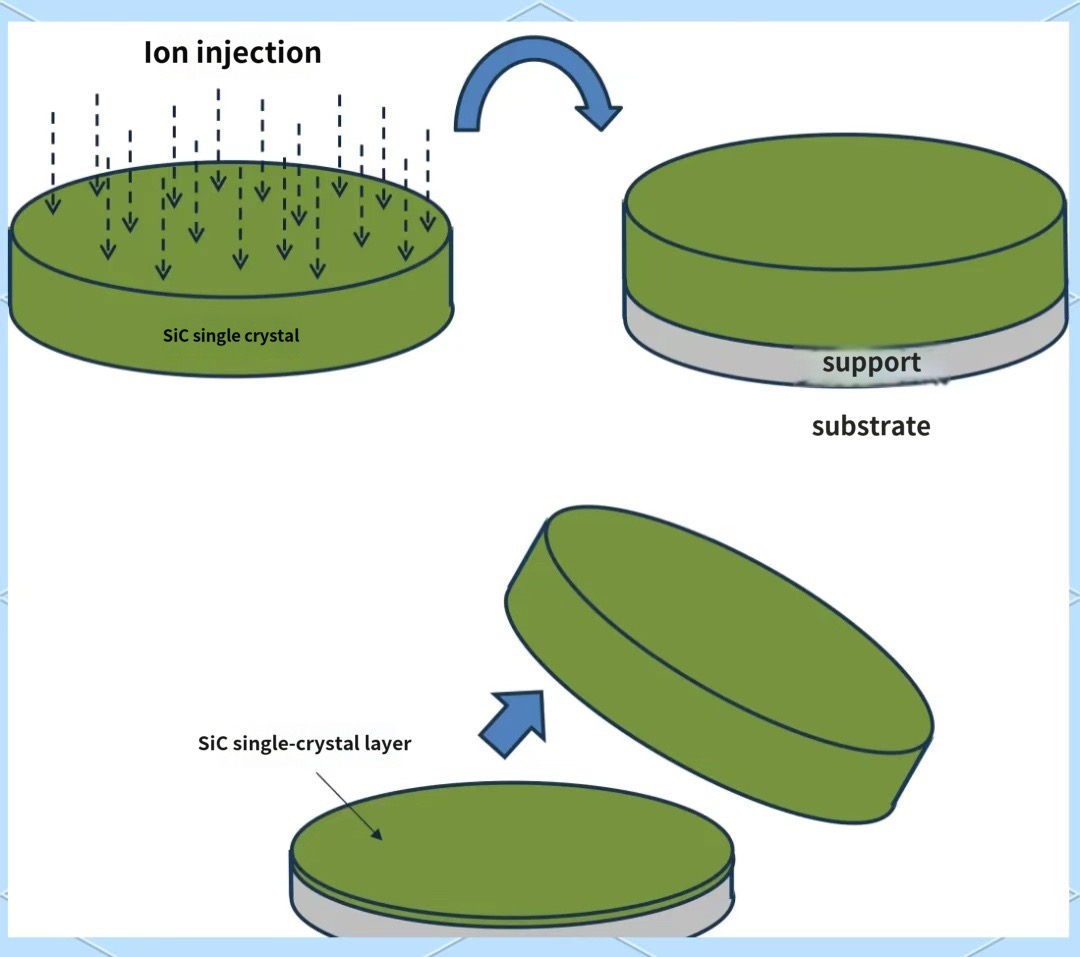

ရိုးရာ slicing လုပ်ငန်းစဉ်များအပြင်၊ SiC wafers များပြင်ဆင်ရန် ဆန်းသစ်သောနည်းလမ်းတွင် bonding နည်းပညာပါဝင်သည်။ ဤချဉ်းကပ်မှုသည် ပါးလွှာသော SiC single-crystal အလွှာကို heterogeneous substrate (supporting substrate) နှင့် ချိတ်ဆက်ခြင်းဖြင့် wafer ထုတ်လုပ်မှုကို ဖြစ်စေသည်။

ပုံ ၃ တွင် လုပ်ငန်းစဉ်စီးဆင်းမှုကို ဖော်ပြထားသည်။

ပထမဦးစွာ၊ SiC single-crystal မျက်နှာပြင်ပေါ်တွင် သတ်မှတ်ထားသောအနက်တွင် ဟိုက်ဒရိုဂျင်အိုင်းယွန်းထည့်သွင်းခြင်း သို့မဟုတ် အလားတူနည်းပညာများမှတစ်ဆင့် delamination အလွှာတစ်ခု ဖွဲ့စည်းသည်။ ထို့နောက် ပြုပြင်ထားသော SiC single-crystal ကို ပြားချပ်ချပ်ထောက်ပံ့သည့်အလွှာနှင့် ချိတ်ဆက်ပြီး ဖိအားနှင့် အပူပေးထားသည်။ ၎င်းသည် SiC single-crystal အလွှာကို ထောက်ပံ့သည့်အလွှာပေါ်သို့ အောင်မြင်စွာလွှဲပြောင်းခွဲထုတ်နိုင်စေပါသည်။

ခွဲထုတ်ထားသော SiC အလွှာကို လိုအပ်သော ပြားချပ်မှုရရှိရန် မျက်နှာပြင်ကုသမှုခံယူပြီး နောက်ဆက်တွဲ ချိတ်ဆက်မှုလုပ်ငန်းစဉ်များတွင် ပြန်လည်အသုံးပြုနိုင်သည်။ ရိုးရာ SiC ပုံဆောင်ခဲများကို လှီးဖြတ်ခြင်းနှင့် နှိုင်းယှဉ်ပါက ဤနည်းပညာသည် စျေးကြီးသောပစ္စည်းများအတွက် ၀ယ်လိုအားကို လျှော့ချပေးသည်။ နည်းပညာဆိုင်ရာစိန်ခေါ်မှုများ ရှိနေသော်လည်း၊ ကုန်ကျစရိတ်နည်းပါးသော wafer ထုတ်လုပ်နိုင်စေရန် သုတေသနနှင့် ဖွံ့ဖြိုးတိုးတက်ရေးသည် တက်ကြွစွာ တိုးတက်နေပါသည်။

SiC ၏ မာကျောမှုနှင့် ဓာတုဗေဒဆိုင်ရာ တည်ငြိမ်မှု မြင့်မားခြင်းကြောင့်—အခန်းအပူချိန်တွင် ဓာတ်ပြုမှုများကို ခံနိုင်ရည်ရှိစေသည်—ကြိတ်ခွဲထားသော အပေါက်ငယ်များကို ဖယ်ရှားရန်၊ မျက်နှာပြင်ပျက်စီးမှုကို လျှော့ချရန်၊ ခြစ်ရာများ၊ အပေါက်ငယ်များနှင့် လိမ္မော်ခွံအပေါက်များကို ဖယ်ရှားရန်၊ မျက်နှာပြင်ကြမ်းတမ်းမှုကို လျှော့ချရန်၊ ပြားချပ်မှုကို တိုးတက်ကောင်းမွန်စေရန်နှင့် မျက်နှာပြင်အရည်အသွေးကို မြှင့်တင်ရန် စက်ပိုင်းဆိုင်ရာ ඔප දැමීම လိုအပ်ပါသည်။

အရည်အသွေးမြင့် ඔප දැමීම မျက်နှာပြင်ရရှိရန်အတွက် အောက်ပါတို့ကို လုပ်ဆောင်ရန် လိုအပ်ပါသည်-

ပွတ်တိုက်မှုအမျိုးအစားများကို ချိန်ညှိပါ၊

အမှုန်အရွယ်အစားကို လျှော့ချခြင်း၊

လုပ်ငန်းစဉ် ကန့်သတ်ချက်များကို အကောင်းဆုံးဖြစ်အောင်ပြုလုပ်ခြင်း၊

လုံလောက်သော မာကျောမှုရှိသော ඔප දැමීමပစ္စည်းများနှင့် အပြားများကို ရွေးချယ်ပါ။

ပုံ ၇ တွင် 1 μm ပွတ်တိုက်ပစ္စည်းများဖြင့် နှစ်ဖက်ပွတ်တိုက်ခြင်းသည် 10 μm အတွင်း ပြားချပ်မှုနှင့် အထူပြောင်းလဲမှုကို ထိန်းချုပ်နိုင်ပြီး မျက်နှာပြင်ကြမ်းတမ်းမှုကို 0.25 nm ခန့်အထိ လျှော့ချနိုင်ကြောင်း ပြသထားသည်။

၃.၂ ဓာတုဗေဒဆိုင်ရာ စက်ပိုင်းဆိုင်ရာ ඔප දැමීම (CMP)

ဓာတုစက်ပိုင်းဆိုင်ရာ ඔප දැමීම (CMP) သည် အလွန်သေးငယ်သော အမှုန်အမွှားများကို ပွတ်တိုက်ခြင်းနှင့် ဓာတုဗေဒဆိုင်ရာ ထွင်းထုခြင်းကို ပေါင်းစပ်ပြီး စီမံဆောင်ရွက်နေသော ပစ္စည်းပေါ်တွင် ချောမွေ့ပြီး ပြားချပ်သော မျက်နှာပြင်ကို ဖန်တီးပေးပါသည်။ အခြေခံမူမှာ-

ඔප දැමීමနှင့် ဝေဖာမျက်နှာပြင်အကြားတွင် ဓာတုဓာတ်ပြုမှုတစ်ခု ဖြစ်ပေါ်ပြီး ပျော့ပျောင်းသောအလွှာတစ်ခုကို ဖွဲ့စည်းပေးသည်။

ပွတ်တိုက်သည့် အမှုန်အမွှားများနှင့် ပျော့ပျောင်းသောအလွှာကြား ပွတ်တိုက်မှုကြောင့် ပစ္စည်းကို ဖယ်ရှားပစ်ပါသည်။

CMP အားသာချက်များ

စက်ပိုင်းဆိုင်ရာ သို့မဟုတ် ဓာတုဗေဒဆိုင်ရာ ඔප දැමීම၏ အားနည်းချက်များကို ကျော်လွှားနိုင်ခြင်း၊

ကမ္ဘာလုံးဆိုင်ရာနှင့် ဒေသတွင်း နှစ်မျိုးလုံးတွင် ပြားချပ်ချပ်ဖြစ်အောင် ပြုလုပ်နိုင်ခြင်း၊

မျက်နှာပြင်များ ပြားချပ်ပြီး ကြမ်းတမ်းမှုနည်းသော မျက်နှာပြင်များကို ထုတ်လုပ်ပေးသည်။

မျက်နှာပြင် သို့မဟုတ် မြေအောက်ပိုင်း ပျက်စီးမှု မကျန်ရှိပါ။

အသေးစိတ်အားဖြင့်-

ဖိအားအောက်တွင် ဝေဖာသည် ඔප දැමීමနှင့် နှိုင်းယှဉ်လျှင် ရွေ့လျားသည်။

အရည်ပျော်တွင်ပါဝင်သော နာနိုမီတာစကေး ပွတ်တိုက်ပစ္စည်းများ (ဥပမာ SiO₂) သည် ပွတ်တိုက်ခြင်း၊ Si–C ကော်ဗယ်လင်နှောင်ကြိုးများကို အားနည်းစေခြင်းနှင့် ပစ္စည်းဖယ်ရှားခြင်းကို မြှင့်တင်ပေးခြင်းတို့တွင် ပါဝင်ပါသည်။

CMP နည်းစနစ်အမျိုးအစားများ-

အခမဲ့ပွတ်တိုက်ခြင်း- ပွတ်တိုက်ပစ္စည်းများ (ဥပမာ SiO₂) ကို အရည်ပျော်တွင် ဆိုင်းငံ့ထားသည်။ ပစ္စည်းဖယ်ရှားခြင်းသည် ခန္ဓာကိုယ်သုံးခုပွတ်တိုက်ခြင်း (wafer–pad–ပွတ်တိုက်ခြင်း) မှတစ်ဆင့် ဖြစ်ပေါ်သည်။ ပွတ်တိုက်မှုအရွယ်အစား (ပုံမှန်အားဖြင့် 60–200 nm)၊ pH နှင့် အပူချိန်တို့ကို တသမတ်တည်းဖြစ်အောင် တိကျစွာထိန်းချုပ်ရမည်။

ပုံသေ ပွတ်တိုက်ခြင်း- ပွတ်တိုက်ပစ္စည်းများ စုပုံခြင်းကို ကာကွယ်ရန်အတွက် ပွတ်တိုက်ပစ္စည်းများကို ပွတ်တိုက်ပြားထဲတွင် ထည့်သွင်းထားသည်—မြင့်မားသော တိကျမှုရှိသော လုပ်ငန်းစဉ်အတွက် အသင့်တော်ဆုံးဖြစ်သည်။

ඔප දැමීමပြီးနောက် သန့်ရှင်းရေး-

ඔප දැමීම ဝေဖာများသည် အောက်ပါတို့ကို ကြုံတွေ့ရသည်-

ဓာတုဗေဒဆိုင်ရာ သန့်ရှင်းရေး (DI ရေနှင့် အညစ်အကြေး အကြွင်းအကျန်များ ဖယ်ရှားခြင်း အပါအဝင်)၊

DI ရေဆေးခြင်းနှင့်

နိုက်ထရိုဂျင်ပူပူဖြင့် အခြောက်ခံခြင်း

မျက်နှာပြင်ညစ်ညမ်းမှုများကို လျှော့ချရန်။

မျက်နှာပြင် အရည်အသွေးနှင့် စွမ်းဆောင်ရည်

မျက်နှာပြင်ကြမ်းတမ်းမှုကို Ra < 0.3 nm အထိ လျှော့ချနိုင်ပြီး semiconductor epitaxy လိုအပ်ချက်များနှင့် ကိုက်ညီပါသည်။

Global Planarization: ဓာတုဗေဒဆိုင်ရာ ပျော့ပျောင်းစေခြင်းနှင့် စက်ပိုင်းဆိုင်ရာ ဖယ်ရှားခြင်း ပေါင်းစပ်မှုသည် ခြစ်ရာများနှင့် မညီမညာ ထွင်းထုခြင်းများကို လျော့နည်းစေပြီး သန့်စင်သော စက်ပိုင်းဆိုင်ရာ သို့မဟုတ် ဓာတုဗေဒ နည်းလမ်းများထက် ပိုမိုကောင်းမွန်ပါသည်။

မြင့်မားသောစွမ်းဆောင်ရည်- SiC ကဲ့သို့သော မာကျောပြီး ကြွပ်ဆတ်သောပစ္စည်းများအတွက် သင့်လျော်ပြီး ပစ္စည်းဖယ်ရှားမှုနှုန်း 200 nm/h အထက်ရှိသည်။

အခြားပေါ်ပေါက်လာသော ඔප දැමීම နည်းစနစ်များ

CMP အပြင်၊ အခြားနည်းလမ်းများကို အဆိုပြုထားပြီး၊ ၎င်းတို့တွင် အောက်ပါတို့ ပါဝင်သည်။

လျှပ်စစ်ဓာတုဗေဒနည်းဖြင့် ඔප දැමීම၊ ဓာတ်ကူပစ္စည်းများဖြင့် ඔප දැමීම သို့မဟုတ် ထွင်းထုခြင်း နှင့်

ထရိုင်ဘိုဓာတုဗေဒ ඔප දැමීම။

သို့သော်၊ ဤနည်းလမ်းများသည် သုတေသနအဆင့်တွင်သာ ရှိနေသေးပြီး SiC ၏ စိန်ခေါ်မှုရှိသော ပစ္စည်းဂုဏ်သတ္တိများကြောင့် ဖြည်းဖြည်းချင်း တီထွင်ထုတ်လုပ်လာခဲ့ပါသည်။

အဆုံးစွန်အားဖြင့်၊ SiC လုပ်ဆောင်ခြင်းသည် မျက်နှာပြင်အရည်အသွေးတိုးတက်စေရန်အတွက် ကောက်ကွေးမှုနှင့် ကြမ်းတမ်းမှုကို လျှော့ချသည့် တဖြည်းဖြည်းချင်း လုပ်ငန်းစဉ်တစ်ခုဖြစ်ပြီး ပြားချပ်မှုနှင့် ကြမ်းတမ်းမှုထိန်းချုပ်မှုသည် အဆင့်တိုင်းတွင် အရေးကြီးပါသည်။

စီမံဆောင်ရွက်ရေးနည်းပညာ

ဝေဖာကြိတ်ခွဲခြင်းအဆင့်တွင်၊ အမှုန်အရွယ်အစားအမျိုးမျိုးရှိသော စိန်အရည်ကို အသုံးပြု၍ ဝေဖာကို လိုအပ်သော ပြားချပ်မှုနှင့် မျက်နှာပြင်ကြမ်းတမ်းမှုအထိ ကြိတ်ခွဲသည်။ ၎င်းနောက် စက်ပိုင်းဆိုင်ရာနှင့် ဓာတုဗေဒဆိုင်ရာ စက်ပိုင်းဆိုင်ရာ ඔප දැමීම (CMP) နည်းပညာနှစ်မျိုးလုံးကို အသုံးပြု၍ ပျက်စီးမှုကင်းသော ඔප දැමීම දැමීම ဆီလီကွန်ကာဗိုက် (SiC) ဝေဖာများ ထုတ်လုပ်သည်။

ඔප දැමීමပြီးနောက်၊ SiC ဝေဖာများကို အလင်းအမှောင် မိုက်ခရိုစကုပ်များနှင့် X-ray diffractometers ကဲ့သို့သော ကိရိယာများကို အသုံးပြု၍ တင်းကျပ်သော အရည်အသွေးစစ်ဆေးမှုကို ပြုလုပ်ပါသည်။ နောက်ဆုံးတွင်၊ ඔප දැමීමများကို မျက်နှာပြင်ညစ်ညမ်းမှုများကို ဖယ်ရှားရန် အထူးသန့်ရှင်းရေးပစ္စည်းများနှင့် အလွန်သန့်စင်သောရေကို အသုံးပြု၍ သန့်စင်ပါသည်။ ထို့နောက် ၎င်းတို့ကို အလွန်မြင့်မားသော သန့်ရှင်းမှုရှိသော နိုက်ထရိုဂျင်ဓာတ်ငွေ့နှင့် spin dryers များကို အသုံးပြု၍ အခြောက်ခံပြီး ထုတ်လုပ်မှုလုပ်ငန်းစဉ်တစ်ခုလုံးကို ပြီးမြောက်စေပါသည်။

နှစ်ပေါင်းများစွာ ကြိုးပမ်းအားထုတ်မှုများအပြီးတွင် တရုတ်နိုင်ငံအတွင်း SiC single crystal ပြုပြင်ထုတ်လုပ်မှုတွင် သိသာထင်ရှားသော တိုးတက်မှုကို ရရှိခဲ့ပါသည်။ ပြည်တွင်းတွင် 100 mm doped semi-insulating 4H-SiC single crystals များကို အောင်မြင်စွာ တီထွင်ထုတ်လုပ်နိုင်ခဲ့ပြီး n-type 4H-SiC နှင့် 6H-SiC single crystals များကို ယခုအခါ အသုတ်လိုက် ထုတ်လုပ်နိုင်ပြီဖြစ်သည်။ TankeBlue နှင့် TYST ကဲ့သို့သော ကုမ္ပဏီများသည် 150 mm SiC single crystals များကို တီထွင်ထုတ်လုပ်ပြီးဖြစ်သည်။

SiC wafer စီမံဆောင်ရွက်ရေးနည်းပညာအရ ပြည်တွင်းအဖွဲ့အစည်းများသည် ပုံဆောင်ခဲလှီးဖြတ်ခြင်း၊ ကြိတ်ခွဲခြင်းနှင့် ඔප දැමීමအတွက် လုပ်ငန်းစဉ်အခြေအနေများနှင့် လမ်းကြောင်းများကို ကနဦးစူးစမ်းလေ့လာခဲ့ကြသည်။ ၎င်းတို့သည် စက်ပစ္စည်းထုတ်လုပ်ခြင်းအတွက် လိုအပ်ချက်များနှင့် အခြေခံအားဖြင့် ကိုက်ညီသော နမူနာများကို ထုတ်လုပ်နိုင်သည်။ သို့သော် နိုင်ငံတကာစံနှုန်းများနှင့် နှိုင်းယှဉ်ပါက ပြည်တွင်း wafers များ၏ မျက်နှာပြင်စီမံဆောင်ရွက်ရေးအရည်အသွေးသည် သိသိသာသာ နောက်ကျကျန်နေဆဲဖြစ်သည်။ ပြဿနာအချို့ရှိပါသည်-

နိုင်ငံတကာ SiC သီအိုရီများနှင့် လုပ်ငန်းစဉ်နည်းပညာများကို တင်းကျပ်စွာကာကွယ်ထားပြီး အလွယ်တကူရယူနိုင်ခြင်းမရှိပေ။

လုပ်ငန်းစဉ်တိုးတက်မှုနှင့် အကောင်းဆုံးဖြစ်အောင်လုပ်ဆောင်ခြင်းအတွက် သီအိုရီဆိုင်ရာသုတေသနနှင့် ပံ့ပိုးမှု ချို့တဲ့နေပါသည်။

နိုင်ငံခြားမှ စက်ပစ္စည်းများနှင့် အစိတ်အပိုင်းများ တင်သွင်းခြင်း၏ ကုန်ကျစရိတ်မှာ မြင့်မားပါသည်။

စက်ပစ္စည်းဒီဇိုင်း၊ လုပ်ငန်းစဉ်တိကျမှုနှင့် ပစ္စည်းများအပေါ် ပြည်တွင်းသုတေသနသည် နိုင်ငံတကာအဆင့်များနှင့် နှိုင်းယှဉ်ပါက သိသာထင်ရှားသော ကွာဟချက်များကို ပြသနေဆဲဖြစ်သည်။

လက်ရှိတွင် တရုတ်နိုင်ငံတွင် အသုံးပြုသော မြင့်မားသောတိကျမှုရှိသော တူရိယာအများစုကို ပြည်ပမှ တင်သွင်းသည်။ စမ်းသပ်ကိရိယာများနှင့် နည်းစနစ်များသည်လည်း နောက်ထပ်တိုးတက်ကောင်းမွန်ရန် လိုအပ်ပါသည်။

တတိယမျိုးဆက် တစ်ပိုင်းလျှပ်ကူးပစ္စည်းများ စဉ်ဆက်မပြတ် ဖွံ့ဖြိုးတိုးတက်မှုနှင့်အတူ SiC single crystal substrates များ၏ အချင်းသည် တဖြည်းဖြည်း မြင့်တက်လာနေပြီး မျက်နှာပြင် စီမံဆောင်ရွက်မှု အရည်အသွေးအတွက် လိုအပ်ချက်များ မြင့်မားလာပါသည်။ Wafer စီမံဆောင်ရွက်မှု နည်းပညာသည် SiC single crystal ကြီးထွားမှုပြီးနောက် နည်းပညာအရ အခက်ခဲဆုံး ခြေလှမ်းများထဲမှ တစ်ခုဖြစ်လာခဲ့သည်။

လုပ်ငန်းစဉ်တွင် လက်ရှိစိန်ခေါ်မှုများကို ဖြေရှင်းရန်အတွက် ဖြတ်တောက်ခြင်း၊ ကြိတ်ခွဲခြင်းနှင့် ඔප දැමීමတွင် ပါဝင်သော ယန္တရားများကို ပိုမိုလေ့လာရန်နှင့် SiC ဝေဖာထုတ်လုပ်မှုအတွက် သင့်လျော်သော လုပ်ငန်းစဉ်နည်းလမ်းများနှင့် လမ်းကြောင်းများကို စူးစမ်းလေ့လာရန် အရေးကြီးပါသည်။ တစ်ချိန်တည်းမှာပင်၊ အဆင့်မြင့်နိုင်ငံတကာ လုပ်ငန်းစဉ်နည်းပညာများမှ သင်ယူပြီး အရည်အသွေးမြင့် အောက်ခံများထုတ်လုပ်ရန်အတွက် ခေတ်မီ အလွန်တိကျသော စက်ပိုင်းဆိုင်ရာနည်းစနစ်များနှင့် ပစ္စည်းကိရိယာများကို လက်ခံကျင့်သုံးရန် လိုအပ်ပါသည်။

wafer အရွယ်အစား ကြီးလာသည်နှင့်အမျှ ပုံဆောင်ခဲများ ကြီးထွားခြင်းနှင့် ပြုပြင်ခြင်း၏ အခက်အခဲလည်း မြင့်တက်လာပါသည်။ သို့သော်၊ downstream devices များ၏ ထုတ်လုပ်မှု စွမ်းဆောင်ရည်သည် သိသိသာသာ တိုးတက်လာပြီး ယူနစ်ကုန်ကျစရိတ် လျော့ကျသွားသည်။ လက်ရှိတွင် ကမ္ဘာတစ်ဝှမ်းရှိ အဓိက SiC wafer ပေးသွင်းသူများသည် အချင်း ၄ လက်မမှ ၆ လက်မအထိ ထုတ်ကုန်များကို ပေးဆောင်ကြသည်။ Cree နှင့် II-VI ကဲ့သို့သော ဦးဆောင်ကုမ္ပဏီများသည် ၈ လက်မ SiC wafer ထုတ်လုပ်မှုလိုင်းများ ဖွံ့ဖြိုးတိုးတက်ရေးအတွက် စီစဉ်နေပြီဖြစ်သည်။

ပို့စ်တင်ချိန်: ၂၀၂၅ ခုနှစ်၊ မေလ ၂၃ ရက်