၁၉၆၅ ခုနှစ်တွင် Intel ပူးတွဲတည်ထောင်သူ Gordon Moore သည် “Moore's Law” ဖြစ်လာသည့်အရာကို ရှင်းလင်းစွာဖော်ပြခဲ့သည်။ ၎င်းသည် ရာစုနှစ်ဝက်ကျော်ကြာ integrated-circuit (IC) စွမ်းဆောင်ရည်တွင် တည်ငြိမ်သောတိုးတက်မှုများနှင့် ကုန်ကျစရိတ်များကျဆင်းလာခြင်း—ခေတ်မီဒစ်ဂျစ်တယ်နည်းပညာ၏ အခြေခံအုတ်မြစ်—ကို အခြေခံခဲ့သည်။ အတိုချုပ်ပြောရလျှင်- ချစ်ပ်ပေါ်ရှိ ထရန်စစ္စတာအရေအတွက်သည် နှစ်နှစ်တစ်ကြိမ်ခန့် နှစ်ဆတိုးလာသည်။

နှစ်ပေါင်းများစွာ တိုးတက်မှုက အဲဒီ cadence ကို ခြေရာခံခဲ့ပါတယ်။ အခုတော့ အခြေအနေက ပြောင်းလဲနေပါပြီ။ နောက်ထပ် ကျုံ့ဝင်မှုတွေက ပိုခက်ခဲလာပြီး feature size တွေက nanometer အနည်းငယ်အထိ ကျဆင်းသွားပါတယ်။ အင်ဂျင်နီယာတွေဟာ ရုပ်ပိုင်းဆိုင်ရာ ကန့်သတ်ချက်တွေ၊ ပိုမိုရှုပ်ထွေးတဲ့ လုပ်ငန်းစဉ်အဆင့်တွေနဲ့ ကုန်ကျစရိတ်တွေ မြင့်တက်လာတဲ့ အခြေအနေတွေနဲ့ ရင်ဆိုင်နေရပါတယ်။ geometries သေးငယ်တာတွေကလည်း အထွက်နှုန်းကို လျော့ကျစေပြီး ပမာဏများများ ထုတ်လုပ်မှု ပိုခက်ခဲစေပါတယ်။ ထိပ်တန်းစက်ရုံတစ်ခု တည်ဆောက်ခြင်းနဲ့ လည်ပတ်ခြင်းဟာ ကြီးမားတဲ့ အရင်းအနှီးနဲ့ ကျွမ်းကျင်မှုတွေ လိုအပ်ပါတယ်။ ဒါကြောင့် လူအများက Moore's Law ဟာ အရှိန်အဟုန် ကျဆင်းနေတယ်လို့ ငြင်းခုံကြပါတယ်။

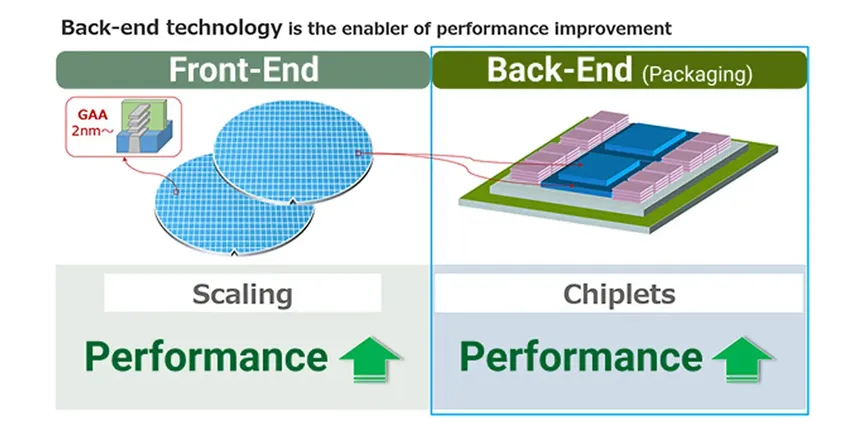

ထိုပြောင်းလဲမှုက chiplets ဟုခေါ်သော ချဉ်းကပ်မှုအသစ်တစ်ခုအတွက် တံခါးဖွင့်ပေးခဲ့သည်။

ချစ်ပ်လက်ဆိုသည်မှာ သီးခြားလုပ်ဆောင်ချက်တစ်ခုကို လုပ်ဆောင်သည့် သေးငယ်သော ဒိုင်းတစ်ခုဖြစ်ပြီး ယခင်က တစ်ခုတည်းသော ချစ်ပ်၏ အစိတ်အပိုင်းတစ်ခုဖြစ်သည်။ ချစ်ပ်လက်များစွာကို တစ်ခုတည်းသော ပက်ကေ့ဂျ်တွင် ပေါင်းစပ်ခြင်းဖြင့် ထုတ်လုပ်သူများသည် စနစ်တစ်ခုလုံးကို တပ်ဆင်နိုင်သည်။

တစ်တုံးတည်းသောခေတ်တွင် လုပ်ဆောင်ချက်အားလုံးသည် ကြီးမားသော die တစ်ခုတည်းတွင် တည်ရှိသောကြောင့် မည်သည့်နေရာတွင်မဆို ချို့ယွင်းချက်တစ်ခုရှိပါက ချစ်ပ်တစ်ခုလုံးကို ဖျက်ဆီးပစ်နိုင်သည်။ ချစ်ပ်လက်များဖြင့် စနစ်များကို “ကောင်းမွန်သော die” (KGD) မှ တည်ဆောက်ထားပြီး အထွက်နှုန်းနှင့် ထုတ်လုပ်မှုထိရောက်မှုကို သိသိသာသာ မြှင့်တင်ပေးပါသည်။

မတူညီသောပေါင်းစပ်မှု—ကွဲပြားသောလုပ်ငန်းစဉ် node များနှင့်ကွဲပြားသောလုပ်ဆောင်ချက်များအတွက်တည်ဆောက်ထားသော dies များကိုပေါင်းစပ်ခြင်း—သည် chiplet များကိုအထူးအစွမ်းထက်စေသည်။ မြင့်မားသောစွမ်းဆောင်ရည်ရှိသော compute block များသည်နောက်ဆုံးပေါ် node များကိုအသုံးပြုနိုင်သော်လည်း memory နှင့် analog circuit များသည် ရင့်ကျက်ပြီးကုန်ကျစရိတ်သက်သာသောနည်းပညာများတွင်ရှိနေပါသည်။ ရလဒ်- ကုန်ကျစရိတ်နည်းပါးစွာဖြင့် မြင့်မားသောစွမ်းဆောင်ရည်။

မော်တော်ကားလုပ်ငန်းက အထူးစိတ်ဝင်စားနေပါတယ်။ အဓိက မော်တော်ကားထုတ်လုပ်သူတွေဟာ ဒီနည်းပညာတွေကို အသုံးပြုပြီး အနာဂတ် မော်တော်ကားအတွင်း SoC တွေကို တီထွင်နေကြပြီး ၂၀၃၀ နောက်ပိုင်းမှာတော့ အစုလိုက်အပြုံလိုက် အသုံးပြုမှုကို ပစ်မှတ်ထားပါတယ်။ Chiplet တွေက သူတို့ကို AI နဲ့ ဂရပ်ဖစ်တွေကို ပိုမိုထိရောက်စွာ ချိန်ညှိနိုင်စေပြီး အထွက်နှုန်းကိုလည်း တိုးတက်စေကာ မော်တော်ကားတစ်ပိုင်းလျှပ်ကူးပစ္စည်းတွေမှာ စွမ်းဆောင်ရည်နဲ့ လုပ်ဆောင်နိုင်စွမ်း နှစ်မျိုးလုံးကို မြှင့်တင်ပေးပါတယ်။

မော်တော်ကားအစိတ်အပိုင်းအချို့သည် တင်းကျပ်သောလုပ်ဆောင်ချက်-ဘေးကင်းရေးစံနှုန်းများနှင့် ကိုက်ညီရမည်ဖြစ်ပြီး ထို့ကြောင့် အဟောင်းများ၊ သက်သေပြထားသော node များကို အားကိုးရမည်ဖြစ်သည်။ တစ်ချိန်တည်းမှာပင်၊ အဆင့်မြင့်ယာဉ်မောင်းအကူအညီ (ADAS) နှင့် software-defined vehicles (SDVs) ကဲ့သို့သော ခေတ်မီစနစ်များသည် တွက်ချက်မှုပိုမိုလိုအပ်ပါသည်။ Chiplets များသည် ထိုကွာဟချက်ကို ဖြည့်ဆည်းပေးသည်- ဘေးကင်းရေးအဆင့် မိုက်ခရိုကွန်ထရိုလာများ၊ ကြီးမားသော မှတ်ဉာဏ်နှင့် အစွမ်းထက်သော AI accelerators များကို ပေါင်းစပ်ခြင်းဖြင့် ထုတ်လုပ်သူများသည် SoC များကို မော်တော်ကားထုတ်လုပ်သူတစ်ဦးချင်းစီ၏ လိုအပ်ချက်များနှင့် ပိုမိုမြန်ဆန်စွာ လိုက်လျောညီထွေဖြစ်အောင် ပြုလုပ်နိုင်သည်။

ဤအားသာချက်များသည် မော်တော်ကားများထက် ကျော်လွန်ပါသည်။ Chiplet ဗိသုကာလက်ရာများသည် AI၊ တယ်လီကွန်းနှင့် အခြားနယ်ပယ်များထဲသို့ ပျံ့နှံ့သွားပြီး စက်မှုလုပ်ငန်းများတစ်လျှောက်တွင် ဆန်းသစ်တီထွင်မှုကို အရှိန်မြှင့်တင်ပေးကာ semiconductor လမ်းပြမြေပုံ၏ အဓိကအချက်အချာတစ်ခု ဖြစ်လာနေပါသည်။

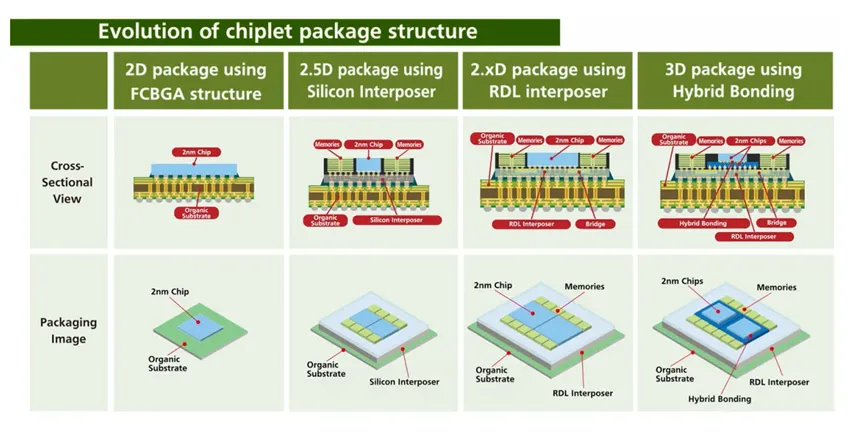

Chiplet ပေါင်းစပ်မှုသည် ကျစ်လစ်သိပ်သည်းပြီး မြန်နှုန်းမြင့် die-to-die ချိတ်ဆက်မှုများပေါ်တွင် မူတည်ပါသည်။ အဓိက enabler မှာ interposer ဖြစ်ပြီး သေးငယ်သော circuit board ကဲ့သို့ပင် signal များကို လမ်းကြောင်းပေးသည့် die များအောက်တွင် မကြာခဏ ဆီလီကွန်ဖြစ်သည့် အလယ်အလတ်အလွှာတစ်ခုဖြစ်သည်။ ပိုမိုကောင်းမွန်သော interposer များသည် ပိုမိုတင်းကျပ်သော ချိတ်ဆက်မှုနှင့် ပိုမိုမြန်ဆန်သော signal ဖလှယ်မှုကို ဆိုလိုသည်။

အဆင့်မြင့်ထုပ်ပိုးမှုကလည်း ပါဝါပေးပို့မှုကို တိုးတက်ကောင်းမွန်စေသည်။ ဒိုင်များအကြား သေးငယ်သောသတ္တုချိတ်ဆက်မှုများ၏ သိပ်သည်းသောအစုအဝေးများသည် ကျဉ်းမြောင်းသောနေရာများတွင်ပင် လျှပ်စီးကြောင်းနှင့်ဒေတာအတွက် လုံလောက်သောလမ်းကြောင်းများကို ပံ့ပိုးပေးပြီး ကန့်သတ်ထားသောထုပ်ပိုးဧရိယာကို ထိရောက်စွာအသုံးပြုနိုင်စဉ်တွင် မြင့်မားသော bandwidth လွှဲပြောင်းမှုကို ဖြစ်စေသည်။

ယနေ့ခေတ် အဓိကချဉ်းကပ်မှုမှာ 2.5D ပေါင်းစပ်မှုဖြစ်သည်- interposer ပေါ်တွင် dies များစွာကို ဘေးချင်းယှဉ်ထားခြင်းဖြစ်သည်။ နောက်ထပ်ခုန်ပျံကျော်လွှားမှုတစ်ခုမှာ 3D ပေါင်းစပ်မှုဖြစ်ပြီး၊ ပိုမြင့်မားသောသိပ်သည်းဆအတွက် through-silicon vias (TSVs) ကို အသုံးပြု၍ dies များကို ဒေါင်လိုက်စီထားသည်။

မော်ဂျူလာချစ်ပ်ဒီဇိုင်း (လုပ်ဆောင်ချက်များနှင့် ဆားကစ်အမျိုးအစားများကို ခွဲထုတ်ခြင်း) ကို 3D stacking နှင့် ပေါင်းစပ်ခြင်းဖြင့် ပိုမိုမြန်ဆန်၊ သေးငယ်၊ ပိုမိုစွမ်းအင်ချွေတာသော semiconductors များကို ရရှိစေသည်။ မှတ်ဉာဏ်နှင့် တွက်ချက်မှုကို ပူးတွဲလုပ်ဆောင်ခြင်းသည် ကြီးမားသောဒေတာစုများသို့ ကြီးမားသော bandwidth ကို ပေးစွမ်းပြီး AI နှင့် အခြားမြင့်မားသောစွမ်းဆောင်ရည်ရှိသော workloads များအတွက် အသင့်တော်ဆုံးဖြစ်သည်။

သို့သော် ဒေါင်လိုက် stacking သည် စိန်ခေါ်မှုများကို ယူဆောင်လာပါသည်။ အပူသည် ပိုမိုလွယ်ကူစွာ စုပုံလာပြီး အပူချိန်စီမံခန့်ခွဲမှုနှင့် ထွက်နှုန်းကို ရှုပ်ထွေးစေသည်။ ယင်းကို ဖြေရှင်းရန်အတွက် သုတေသီများသည် အပူချိန်ကန့်သတ်ချက်များကို ပိုမိုကောင်းမွန်စွာ ကိုင်တွယ်ဖြေရှင်းနိုင်ရန် ထုပ်ပိုးမှုနည်းလမ်းအသစ်များကို တီထွင်နေကြသည်။ ထိုသို့ပင်ဖြစ်သော်လည်း အရှိန်အဟုန်မှာ အားကောင်းနေဆဲဖြစ်သည်- chiplets နှင့် 3D ပေါင်းစပ်မှု ပေါင်းစပ်မှုကို Moore's Law မှ ထွက်ခွာသွားသည့်နေရာတွင် မီးရှူးတိုင်ကို သယ်ဆောင်ရန် အသင့်ဖြစ်နေသော ပုံစံတစ်ခုအဖြစ် ကျယ်ကျယ်ပြန့်ပြန့် ရှုမြင်ကြသည်။

ပို့စ်တင်ချိန်: ၂၀၂၅ ခုနှစ်၊ အောက်တိုဘာလ ၁၅ ရက်