SiC ဝေဖာ၏ အနှစ်ချုပ်

ဆီလီကွန်ကာဗိုက် (SiC) ဝေဖာများမော်တော်ကား၊ ပြန်လည်ပြည့်ဖြိုးမြဲစွမ်းအင်နှင့် အာကာသကဏ္ဍများတွင် မြင့်မားသောပါဝါ၊ မြင့်မားသောကြိမ်နှုန်းနှင့် မြင့်မားသောအပူချိန် အီလက်ထရွန်းနစ်ပစ္စည်းများအတွက် ရွေးချယ်မှုအခြေခံဖြစ်လာခဲ့သည်။ ကျွန်ုပ်တို့၏ အစုစုတွင် အဓိက polytype များနှင့် doping စနစ်များ—နိုက်ထရိုဂျင် doped 4H (4H-N)၊ မြင့်မားသောသန့်စင်မှု semi-insulating (HPSI)၊ နိုက်ထရိုဂျင် doped 3C (3C-N) နှင့် p-type 4H/6H (4H/6H-P)—ပါဝင်ပြီး အရည်အသွေးအဆင့်သုံးမျိုးဖြင့် ရရှိနိုင်ပါသည်- PRIME (အပြည့်အဝ ඔප දැමීම၊ device-grade substrates)၊ DUMMY (လုပ်ငန်းစဉ်စမ်းသပ်မှုများအတွက် lapped သို့မဟုတ် unpolished) နှင့် RESEARCH (R&D အတွက် စိတ်ကြိုက် epi layer များနှင့် doping profile များ)။ wafer အချင်းများသည် 2″၊ 4″၊ 6″၊ 8″ နှင့် 12″ အထိ ရှိသည်။ ကျွန်ုပ်တို့သည် in-house crystal ကြီးထွားမှုကို ပံ့ပိုးရန်အတွက် monocrystalline boules များနှင့် တိကျစွာ ဦးတည်ထားသော seed crystals များကိုလည်း ထောက်ပံ့ပေးပါသည်။

ကျွန်ုပ်တို့၏ 4H-N wafers များတွင် 1×10¹⁶ မှ 1×10¹⁹ cm⁻³ အထိ carrier densities များနှင့် 0.01–10 Ω·cm resistivities များပါရှိပြီး 2 MV/cm အထက်ရှိ electron mobility နှင့် breakdown fields များကို ပေးစွမ်းနိုင်သည်—Schottky diode များ၊ MOSFETs နှင့် JFETs များအတွက် အသင့်တော်ဆုံးဖြစ်သည်။ HPSI substrates များသည် 1×10¹² Ω·cm resistivity ထက်ကျော်လွန်ပြီး micropipe densities များသည် 0.1 cm⁻² အောက်ရှိသောကြောင့် RF နှင့် microwave devices များအတွက် leakage အနည်းဆုံးဖြစ်စေသည်။ 2″ နှင့် 4″ formats များဖြင့် ရရှိနိုင်သော Cubic 3C-N သည် silicon ပေါ်တွင် heteroepitaxy ကိုဖွင့်ပေးပြီး photonic နှင့် MEMS applications အသစ်များကို ပံ့ပိုးပေးသည်။ 1×10¹⁶–5×10¹⁸ cm⁻³ အထိ aluminum ဖြင့်ပြုလုပ်ထားသော P-type 4H/6H-P wafers များသည် complementary device architectures များကို အထောက်အကူပြုသည်။

SiC wafer၊ PRIME wafer များသည် <0.2 nm RMS မျက်နှာပြင်ကြမ်းတမ်းမှု၊ စုစုပေါင်းအထူပြောင်းလဲမှု 3 µm အောက်နှင့် bow <10 µm အထိ ဓာတု-စက်ပိုင်းဆိုင်ရာ ඔප දැමීමများကို ပြုလုပ်ကြသည်။ DUMMY အောက်ခံများသည် တပ်ဆင်ခြင်းနှင့် ထုပ်ပိုးခြင်းစမ်းသပ်မှုများကို အရှိန်မြှင့်ပေးပြီး RESEARCH wafer များတွင် epi-layer အထူ 2–30 µm နှင့် bespoke doping ပါရှိသည်။ ထုတ်ကုန်အားလုံးကို X-ray diffraction (rocking curve <30 arcsec) နှင့် Raman spectroscopy ဖြင့် အသိအမှတ်ပြုထားပြီး လျှပ်စစ်စမ်းသပ်မှုများ—Hall တိုင်းတာမှုများ၊ C–V profiling နှင့် micropipe scanning—ဖြင့် JEDEC နှင့် SEMI ကိုက်ညီမှုကို သေချာစေသည်။

၁၅၀ မီလီမီတာ အချင်းအထိရှိသော ဘောလ်များကို PVT နှင့် CVD မှတစ်ဆင့် 1×10³ cm⁻² အောက် dislocation densities ရှိပြီး micropipe အရေအတွက်နည်းသော စိုက်ပျိုးမှုဖြင့် စိုက်ပျိုးကြသည်။ မျိုးစေ့ပုံဆောင်ခဲများကို c-axis ၏ 0.1° အတွင်း ဖြတ်တောက်ပြီး ပြန်လည်ပွားများနိုင်သော ကြီးထွားမှုနှင့် မြင့်မားသော လှီးဖြတ်မှုအထွက်နှုန်းကို အာမခံပါသည်။

မျိုးစုံသော polytype များ၊ doping variants များ၊ အရည်အသွေးအဆင့်များ၊ SiC wafer အရွယ်အစားများနှင့် ကုမ္ပဏီတွင်း boule နှင့် seed-crystal ထုတ်လုပ်မှုတို့ကို ပေါင်းစပ်ခြင်းဖြင့် ကျွန်ုပ်တို့၏ SiC substrate platform သည် ထောက်ပံ့ရေးကွင်းဆက်များကို ချောမွေ့စေပြီး လျှပ်စစ်ယာဉ်များ၊ smart grid များနှင့် harsh-environment application များအတွက် စက်ပစ္စည်းဖွံ့ဖြိုးတိုးတက်မှုကို အရှိန်မြှင့်တင်ပေးသည်။

SiC ဝေဖာ၏ အနှစ်ချုပ်

ဆီလီကွန်ကာဗိုက် (SiC) ဝေဖာများမော်တော်ကား၊ ပြန်လည်ပြည့်ဖြိုးမြဲစွမ်းအင်နှင့် အာကာသကဏ္ဍများတွင် မြင့်မားသောပါဝါ၊ မြင့်မားသောကြိမ်နှုန်းနှင့် မြင့်မားသောအပူချိန် အီလက်ထရွန်းနစ်ပစ္စည်းများအတွက် ရွေးချယ်မှု SiC အောက်ခံဖြစ်လာခဲ့သည်။ ကျွန်ုပ်တို့၏ အစုစုတွင် အဓိက polytype များနှင့် doping အစီအစဉ်များ—နိုက်ထရိုဂျင် doped 4H (4H-N)၊ မြင့်မားသောသန့်စင်မှု semi-insulating (HPSI)၊ နိုက်ထရိုဂျင် doped 3C (3C-N) နှင့် p-type 4H/6H (4H/6H-P)—ပါဝင်သည်—အရည်အသွေးအဆင့်သုံးမျိုးဖြင့် ရရှိနိုင်ပါသည်- SiC waferPRIME (အပြည့်အဝ ඔප දැමීම၊ စက်ပစ္စည်းအဆင့် အောက်ခံများ)၊ DUMMY (လုပ်ငန်းစဉ်စမ်းသပ်မှုများအတွက် ඔප දැමී သို့မဟုတ် မදැමීම) နှင့် RESEARCH (သုတေသနနှင့် ဖွံ့ဖြိုးတိုးတက်ရေးအတွက် စိတ်ကြိုက် epi အလွှာများနှင့် doping ပရိုဖိုင်များ)။ SiC Wafer အချင်းများသည် ရိုးရာကိရိယာများနှင့် အဆင့်မြင့်စက်ရုံနှစ်ခုလုံးနှင့် ကိုက်ညီစေရန် ၂ လက်မ၊ ၄ လက်မ၊ ၆ လက်မ၊ ၈ လက်မနှင့် ၁၂ လက်မအထိ ရှိသည်။ ကျွန်ုပ်တို့သည် monocrystalline boules များနှင့် တိကျစွာ ဦးတည်ထားသော seed crystals များကိုလည်း ထောက်ပံ့ပေးပါသည်။

ကျွန်ုပ်တို့၏ 4H-N SiC wafers များတွင် 1×10¹⁶ မှ 1×10¹⁹ cm⁻³ အထိ carrier densities များနှင့် 0.01–10 Ω·cm resistivities များပါရှိပြီး 2 MV/cm အထက်ရှိ electron mobility နှင့် breakdown fields များကို ပေးစွမ်းနိုင်သည်—Schottky diode များ၊ MOSFETs နှင့် JFETs များအတွက် အသင့်တော်ဆုံးဖြစ်သည်။ HPSI substrates များသည် 0.1 cm⁻² အောက်ရှိ micropipe densities များဖြင့် 1×10¹² Ω·cm resistivity ထက်ကျော်လွန်ပြီး RF နှင့် microwave devices များအတွက် leakage အနည်းဆုံးဖြစ်စေရန် သေချာစေသည်။ 2″ နှင့် 4″ formats များဖြင့် ရရှိနိုင်သော Cubic 3C-N သည် silicon ပေါ်တွင် heteroepitaxy ကိုဖွင့်ပေးပြီး photonic နှင့် MEMS applications အသစ်များကို ပံ့ပိုးပေးသည်။ SiC wafer P-type 4H/6H-P wafers များကို 1×10¹⁶–5×10¹⁸ cm⁻³ အထိ အလူမီနီယမ်ဖြင့် ပြုလုပ်ထားပြီး complementary device architectures များကို အထောက်အကူပြုသည်။

SiC wafer PRIME wafer များသည် <0.2 nm RMS မျက်နှာပြင်ကြမ်းတမ်းမှု၊ စုစုပေါင်းအထူပြောင်းလဲမှု 3 µm အောက်နှင့် bow <10 µm အထိ ဓာတု-စက်ပိုင်းဆိုင်ရာ ඔප දැමීම ပြုလုပ်ကြသည်။ DUMMY အောက်ခံများသည် တပ်ဆင်ခြင်းနှင့် ထုပ်ပိုးခြင်းစမ်းသပ်မှုများကို အရှိန်မြှင့်ပေးပြီး၊ RESEARCH wafer များတွင် epi-layer အထူ 2–30 µm နှင့် bespoke doping ပါရှိသည်။ ထုတ်ကုန်အားလုံးကို X-ray diffraction (rocking curve <30 arcsec) နှင့် Raman spectroscopy ဖြင့် အသိအမှတ်ပြုထားပြီး၊ လျှပ်စစ်စမ်းသပ်မှုများ—Hall တိုင်းတာမှုများ၊ C–V profiling နှင့် micropipe scanning—ဖြင့် JEDEC နှင့် SEMI ကိုက်ညီမှုကို သေချာစေသည်။

၁၅၀ မီလီမီတာ အချင်းအထိရှိသော ဘောလ်များကို PVT နှင့် CVD မှတစ်ဆင့် 1×10³ cm⁻² အောက် dislocation densities ရှိပြီး micropipe အရေအတွက်နည်းသော စိုက်ပျိုးမှုဖြင့် စိုက်ပျိုးကြသည်။ မျိုးစေ့ပုံဆောင်ခဲများကို c-axis ၏ 0.1° အတွင်း ဖြတ်တောက်ပြီး ပြန်လည်ပွားများနိုင်သော ကြီးထွားမှုနှင့် မြင့်မားသော လှီးဖြတ်မှုအထွက်နှုန်းကို အာမခံပါသည်။

မျိုးစုံသော polytype များ၊ doping variants များ၊ အရည်အသွေးအဆင့်များ၊ SiC wafer အရွယ်အစားများနှင့် ကုမ္ပဏီတွင်း boule နှင့် seed-crystal ထုတ်လုပ်မှုတို့ကို ပေါင်းစပ်ခြင်းဖြင့် ကျွန်ုပ်တို့၏ SiC substrate platform သည် ထောက်ပံ့ရေးကွင်းဆက်များကို ချောမွေ့စေပြီး လျှပ်စစ်ယာဉ်များ၊ smart grid များနှင့် harsh-environment application များအတွက် စက်ပစ္စည်းဖွံ့ဖြိုးတိုးတက်မှုကို အရှိန်မြှင့်တင်ပေးသည်။

၆ လက်မ 4H-N အမျိုးအစား SiC ဝေဖာ၏ အချက်အလက်စာရွက်

| ၆ လက်မ SiC ဝေဖာဒေတာစာရွက် | ||||

| ကန့်သတ်ချက် | လက်အောက်ခံ ကန့်သတ်ချက် | Z တန်း | P အဆင့် | D အဆင့် |

| အချင်း | ၁၄၉.၅–၁၅၀.၀ မီလီမီတာ | ၁၄၉.၅–၁၅၀.၀ မီလီမီတာ | ၁၄၉.၅–၁၅၀.၀ မီလီမီတာ | |

| အထူ | ၄H-N | ၃၅၀ မိုက်ခရိုမီတာ ± ၁၅ မိုက်ခရိုမီတာ | ၃၅၀ မိုက်ခရိုမီတာ ± ၂၅ မိုက်ခရိုမီတာ | ၃၅၀ မိုက်ခရိုမီတာ ± ၂၅ မိုက်ခရိုမီတာ |

| အထူ | 4H-SI | ၅၀၀ မိုက်ခရိုမီတာ ± ၁၅ မိုက်ခရိုမီတာ | ၅၀၀ မိုက်ခရိုမီတာ ± ၂၅ မိုက်ခရိုမီတာ | ၅၀၀ မိုက်ခရိုမီတာ ± ၂၅ မိုက်ခရိုမီတာ |

| ဝေဖာ ဦးတည်ချက် | ဝင်ရိုးပြင်ပ: <11-20> ဘက်သို့ 4.0° ±0.5° (4H-N); ဝင်ရိုးပေါ်တွင်: <0001> ±0.5° (4H-SI) | ဝင်ရိုးပြင်ပ: <11-20> ဘက်သို့ 4.0° ±0.5° (4H-N); ဝင်ရိုးပေါ်တွင်: <0001> ±0.5° (4H-SI) | ဝင်ရိုးပြင်ပ: <11-20> ဘက်သို့ 4.0° ±0.5° (4H-N); ဝင်ရိုးပေါ်တွင်: <0001> ±0.5° (4H-SI) | |

| မိုက်ခရိုပိုက် သိပ်သည်းဆ | ၄H-N | ≤ ၀.၂ စင်တီမီတာ⁻² | ≤ ၂ စင်တီမီတာ⁻² | ≤ ၁၅ စင်တီမီတာ⁻² |

| မိုက်ခရိုပိုက် သိပ်သည်းဆ | 4H-SI | ≤ ၁ စင်တီမီတာ⁻² | ≤ ၅ စင်တီမီတာ⁻² | ≤ ၁၅ စင်တီမီတာ⁻² |

| ခုခံအား | ၄H-N | ၀.၀၁၅–၀.၀၂၄ အိုမီဂါ·စင်တီမီတာ | ၀.၀၁၅–၀.၀၂၈ အိုမီဂါ·စင်တီမီတာ | ၀.၀၁၅–၀.၀၂၈ အိုမီဂါ·စင်တီမီတာ |

| ခုခံအား | 4H-SI | ≥ 1×10¹⁰ Ω·စင်တီမီတာ | ≥ 1×10⁵ Ω·စင်တီမီတာ | |

| အဓိက ပြားချပ်ချပ် အနေအထား | [၁၀-၁၀] ± ၅.၀° | [၁၀-၁၀] ± ၅.၀° | [၁၀-၁၀] ± ၅.၀° | |

| အဓိကပြားချပ်အရှည် | ၄H-N | ၄၇.၅ မီလီမီတာ ± ၂.၀ မီလီမီတာ | ||

| အဓိကပြားချပ်အရှည် | 4H-SI | အပေါက် | ||

| အနားသတ်ဖယ်ထုတ်ခြင်း | ၃ မီလီမီတာ | |||

| Warp/LTV/TTV/Bow | ≤2.5 µm / ≤6 µm / ≤25 µm / ≤35 µm | ≤5 µm / ≤15 µm / ≤40 µm / ≤60 µm | ||

| ကြမ်းတမ်းမှု | ပိုလန် | Ra ≤ 1 nm | ||

| ကြမ်းတမ်းမှု | စီအမ်ပီ | Ra ≤ 0.2 nm | Ra ≤ 0.5 nm | |

| အနားစွန်း အက်ကွဲကြောင်းများ | မရှိပါ | စုစုပေါင်းအရှည် ≤ ၂၀ မီလီမီတာ၊ တစ်ခုတည်းသော ≤ ၂ မီလီမီတာ | ||

| Hex ပြားများ | စုစုပေါင်းဧရိယာ ≤ 0.05% | စုစုပေါင်းဧရိယာ ≤ 0.1% | စုစုပေါင်းဧရိယာ ≤ 1% | |

| ဘက်စုံအမျိုးအစား ဧရိယာများ | မရှိပါ | စုစုပေါင်းဧရိယာ ≤ ၃% | စုစုပေါင်းဧရိယာ ≤ ၃% | |

| ကာဗွန်ပါဝင်မှုများ | စုစုပေါင်းဧရိယာ ≤ 0.05% | စုစုပေါင်းဧရိယာ ≤ ၃% | ||

| မျက်နှာပြင်ခြစ်ရာများ | မရှိပါ | စုစုပေါင်းအရှည် ≤ 1 × ဝေဖာအချင်း | ||

| အနားသတ်ချစ်ပ်များ | အကျယ်နှင့်အနက် ၀.၂ မီလီမီတာ ထက်ကျော်လွန်၍ ခွင့်မပြုပါ။ | ချစ်ပ် ၇ ခုအထိ၊ တစ်ခုလျှင် ၁ မီလီမီတာ ≤ | ||

| TSD (ချည်မျှင် ဝက်အူ ရွေ့လျားမှု) | ≤ ၅၀၀ စင်တီမီတာ⁻² | မရှိပါ | ||

| BPD (အခြေခံပြားနေရာလွဲခြင်း) | ≤ ၁၀၀၀ စင်တီမီတာ⁻² | မရှိပါ | ||

| မျက်နှာပြင်ညစ်ညမ်းမှု | မရှိပါ | |||

| ထုပ်ပိုးခြင်း | ဝါဖာများစွာပါသော ကက်ဆက် သို့မဟုတ် ဝါဖာတစ်ခုတည်းပါသော ကွန်တိန်နာ | ဝါဖာများစွာပါသော ကက်ဆက် သို့မဟုတ် ဝါဖာတစ်ခုတည်းပါသော ကွန်တိန်နာ | ဝါဖာများစွာပါသော ကက်ဆက် သို့မဟုတ် ဝါဖာတစ်ခုတည်းပါသော ကွန်တိန်နာ | |

၄ လက်မ 4H-N အမျိုးအစား SiC ဝေဖာ၏ အချက်အလက်စာရွက်

| ၄ လက်မ SiC wafer ရဲ့ အချက်အလက်စာရွက် | |||

| ကန့်သတ်ချက် | MPD ထုတ်လုပ်မှု သုည | စံထုတ်လုပ်မှုအဆင့် (P အဆင့်) | အတုအယောင်အဆင့် (D အဆင့်) |

| အချင်း | ၉၉.၅ မီလီမီတာ–၁၀၀.၀ မီလီမီတာ | ||

| အထူ (4H-N) | ၃၅၀ မိုက်ခရိုမီတာ ± ၁၅ မိုက်ခရိုမီတာ | ၃၅၀ မိုက်ခရိုမီတာ ± ၂၅ မိုက်ခရိုမီတာ | |

| အထူ (4H-Si) | ၅၀၀ မိုက်ခရိုမီတာ ± ၁၅ မိုက်ခရိုမီတာ | ၅၀၀ မိုက်ခရိုမီတာ ± ၂၅ မိုက်ခရိုမီတာ | |

| ဝေဖာ ဦးတည်ချက် | ဝင်ရိုးပြင်ပ: 4H-N အတွက် <1120> ဘက်သို့ 4.0° ±0.5°; ဝင်ရိုးပေါ်တွင်: 4H-Si အတွက် <0001> ±0.5° | ||

| မိုက်ခရိုပိုက် သိပ်သည်းဆ (4H-N) | ≤၀.၂ စင်တီမီတာ⁻² | ≤၂ စင်တီမီတာ⁻² | ≤၁၅ စင်တီမီတာ⁻² |

| မိုက်ခရိုပိုက် သိပ်သည်းဆ (4H-Si) | ≤1 စင်တီမီတာ⁻² | ≤၅ စင်တီမီတာ⁻² | ≤၁၅ စင်တီမီတာ⁻² |

| ခုခံအား (4H-N) | ၀.၀၁၅–၀.၀၂၄ အိုမီဂါ·စင်တီမီတာ | ၀.၀၁၅–၀.၀၂၈ အိုမီဂါ·စင်တီမီတာ | |

| ခုခံအား (4H-Si) | ≥1E10 Ω·စင်တီမီတာ | ≥1E5 Ω·စင်တီမီတာ | |

| အဓိက ပြားချပ်ချပ် အနေအထား | [၁၀-၁၀] ±၅.၀° | ||

| အဓိကပြားချပ်အရှည် | ၃၂.၅ မီလီမီတာ ±၂.၀ မီလီမီတာ | ||

| ဒုတိယပြားချပ်အရှည် | ၁၈.၀ မီလီမီတာ ±၂.၀ မီလီမီတာ | ||

| ဒုတိယပြားချပ်ချပ် ಒಟ್ಟಾರೆ | ဆီလီကွန်ကို အပေါ်ဘက်သို့ မျက်နှာမူထားသည်- အဓိကပြားမှ 90° CW ±5.0° | ||

| အနားသတ်ဖယ်ထုတ်ခြင်း | ၃ မီလီမီတာ | ||

| LTV/TTV/Bow Warp | ≤2.5 µm/≤5 µm/≤15 µm/≤30 µm | ≤10 µm/≤15 µm/≤25 µm/≤40 µm | |

| ကြမ်းတမ်းမှု | ပိုလန် Ra ≤1 nm; CMP Ra ≤0.2 nm | Ra ≤0.5 nm | |

| မြင့်မားသော အလင်းကြောင့် အနားစွန်း အက်ကွဲကြောင်းများ | မရှိပါ | မရှိပါ | စုစုပေါင်းအရှည် ≤၁၀ မီလီမီတာ၊ တစ်ခုတည်းသောအရှည် ≤၂ မီလီမီတာ |

| မြင့်မားသောပြင်းထန်မှုအလင်းဖြင့် Hex ပြားများ | စုစုပေါင်းဧရိယာ ≤0.05% | စုစုပေါင်းဧရိယာ ≤0.05% | စုစုပေါင်းဧရိယာ ≤0.1% |

| မြင့်မားသော ပြင်းထန်မှုရှိသော အလင်းရောင်ဖြင့် Polytype ဧရိယာများ | မရှိပါ | စုစုပေါင်းဧရိယာ ≤3% | |

| မြင်သာသော ကာဗွန် ပါဝင်မှုများ | စုစုပေါင်းဧရိယာ ≤0.05% | စုစုပေါင်းဧရိယာ ≤3% | |

| မြင့်မားသော အလင်းကြောင့် ဆီလီကွန် မျက်နှာပြင် ခြစ်ရာများ | မရှိပါ | စုစုပေါင်းအရှည် ≤1 ဝေဖာအချင်း | |

| မြင့်မားသော ပြင်းထန်မှုရှိသော အလင်းရောင်ဖြင့် အနားသတ်ချစ်ပ်များ | အကျယ်နှင့်အနက် ≥၀.၂ မီလီမီတာ ခွင့်မပြုပါ။ | ၅ ခု ခွင့်ပြုထားသည်၊ တစ်ခုလျှင် ၁ မီလီမီတာ ≤ | |

| မြင့်မားသော ပြင်းထန်သော အလင်းရောင်ကြောင့် ဆီလီကွန် မျက်နှာပြင် ညစ်ညမ်းခြင်း | မရှိပါ | ||

| ချည်မျှင် ဝက်အူ ရွေ့လျားမှု | ≤၅၀၀ စင်တီမီတာ⁻² | မရှိပါ | |

| ထုပ်ပိုးခြင်း | ဝါဖာများစွာပါသော ကက်ဆက် သို့မဟုတ် ဝါဖာတစ်ခုတည်းပါသော ကွန်တိန်နာ | ဝါဖာများစွာပါသော ကက်ဆက် သို့မဟုတ် ဝါဖာတစ်ခုတည်းပါသော ကွန်တိန်နာ | ဝါဖာများစွာပါသော ကက်ဆက် သို့မဟုတ် ဝါဖာတစ်ခုတည်းပါသော ကွန်တိန်နာ |

၄ လက်မ HPSI အမျိုးအစား SiC wafer ၏ အချက်အလက်စာရွက်

| ၄ လက်မ HPSI အမျိုးအစား SiC wafer ၏ အချက်အလက်စာရွက် | |||

| ကန့်သတ်ချက် | သုည MPD ထုတ်လုပ်မှုအဆင့် (Z အဆင့်) | စံထုတ်လုပ်မှုအဆင့် (P အဆင့်) | အတုအယောင်အဆင့် (D အဆင့်) |

| အချင်း | ၉၉.၅–၁၀၀.၀ မီလီမီတာ | ||

| အထူ (4H-Si) | ၅၀၀ မိုက်ခရိုမီတာ ±၂၀ မိုက်ခရိုမီတာ | ၅၀၀ မိုက်ခရိုမီတာ ±၂၅ မိုက်ခရိုမီတာ | |

| ဝေဖာ ဦးတည်ချက် | ဝင်ရိုးပြင်ပ: 4H-N အတွက် <11-20> ဘက်သို့ 4.0° ±0.5°; ဝင်ရိုးပေါ်တွင်: 4H-Si အတွက် <0001> ±0.5° | ||

| မိုက်ခရိုပိုက် သိပ်သည်းဆ (4H-Si) | ≤1 စင်တီမီတာ⁻² | ≤၅ စင်တီမီတာ⁻² | ≤၁၅ စင်တီမီတာ⁻² |

| ခုခံအား (4H-Si) | ≥1E9 Ω·စင်တီမီတာ | ≥1E5 Ω·စင်တီမီတာ | |

| အဓိက ပြားချပ်ချပ် အနေအထား | (၁၀-၁၀) ±၅.၀° | ||

| အဓိကပြားချပ်အရှည် | ၃၂.၅ မီလီမီတာ ±၂.၀ မီလီမီတာ | ||

| ဒုတိယပြားချပ်အရှည် | ၁၈.၀ မီလီမီတာ ±၂.၀ မီလီမီတာ | ||

| ဒုတိယပြားချပ်ချပ် ಒಟ್ಟಾರೆ | ဆီလီကွန်ကို အပေါ်ဘက်သို့ မျက်နှာမူထားသည်- အဓိကပြားမှ 90° CW ±5.0° | ||

| အနားသတ်ဖယ်ထုတ်ခြင်း | ၃ မီလီမီတာ | ||

| LTV/TTV/Bow Warp | ≤3 µm/≤5 µm/≤15 µm/≤30 µm | ≤10 µm/≤15 µm/≤25 µm/≤40 µm | |

| ကြမ်းတမ်းမှု (C မျက်နှာပြင်) | ပိုလန် | Ra ≤1 nm | |

| ကြမ်းတမ်းမှု (Si မျက်နှာပြင်) | စီအမ်ပီ | Ra ≤0.2 nm | Ra ≤0.5 nm |

| မြင့်မားသော အလင်းကြောင့် အနားစွန်း အက်ကွဲကြောင်းများ | မရှိပါ | စုစုပေါင်းအရှည် ≤၁၀ မီလီမီတာ၊ တစ်ခုတည်းသောအရှည် ≤၂ မီလီမီတာ | |

| မြင့်မားသောပြင်းထန်မှုအလင်းဖြင့် Hex ပြားများ | စုစုပေါင်းဧရိယာ ≤0.05% | စုစုပေါင်းဧရိယာ ≤0.05% | စုစုပေါင်းဧရိယာ ≤0.1% |

| မြင့်မားသော ပြင်းထန်မှုရှိသော အလင်းရောင်ဖြင့် Polytype ဧရိယာများ | မရှိပါ | စုစုပေါင်းဧရိယာ ≤3% | |

| မြင်သာသော ကာဗွန် ပါဝင်မှုများ | စုစုပေါင်းဧရိယာ ≤0.05% | စုစုပေါင်းဧရိယာ ≤3% | |

| မြင့်မားသော အလင်းကြောင့် ဆီလီကွန် မျက်နှာပြင် ခြစ်ရာများ | မရှိပါ | စုစုပေါင်းအရှည် ≤1 ဝေဖာအချင်း | |

| မြင့်မားသော ပြင်းထန်မှုရှိသော အလင်းရောင်ဖြင့် အနားသတ်ချစ်ပ်များ | အကျယ်နှင့်အနက် ≥၀.၂ မီလီမီတာ ခွင့်မပြုပါ။ | ၅ ခု ခွင့်ပြုထားသည်၊ တစ်ခုလျှင် ၁ မီလီမီတာ ≤ | |

| မြင့်မားသော ပြင်းထန်သော အလင်းရောင်ကြောင့် ဆီလီကွန် မျက်နှာပြင် ညစ်ညမ်းခြင်း | မရှိပါ | မရှိပါ | |

| ချည်မျှင် ဝက်အူ ကွာကျခြင်း | ≤၅၀၀ စင်တီမီတာ⁻² | မရှိပါ | |

| ထုပ်ပိုးခြင်း | ဝါဖာများစွာပါသော ကက်ဆက် သို့မဟုတ် ဝါဖာတစ်ခုတည်းပါသော ကွန်တိန်နာ | ||

SiC wafer ရဲ့ အသုံးချမှု

-

EV အင်ဗာတာများအတွက် SiC ဝေဖာ ပါဝါမော်ဂျူးများ

SiC wafer-based MOSFETs နှင့် အရည်အသွေးမြင့် SiC wafer substrates ပေါ်တွင် တည်ဆောက်ထားသော diodes များသည် အလွန်နည်းပါးသော switching losses များကို ပေးစွမ်းသည်။ SiC wafer နည်းပညာကို အသုံးပြုခြင်းဖြင့် ဤ power module များသည် ပိုမိုမြင့်မားသော voltages နှင့် tempers များတွင် လည်ပတ်ပြီး ပိုမိုထိရောက်သော traction inverters များကို ဖြစ်စေသည်။ SiC wafer dies များကို power stage များထဲသို့ ပေါင်းစပ်ခြင်းဖြင့် အအေးပေးစနစ် လိုအပ်ချက်များနှင့် footprint ကို လျှော့ချပေးပြီး SiC wafer ဆန်းသစ်တီထွင်မှု၏ အလားအလာအပြည့်အဝကို ပြသသည်။ -

SiC Wafer ပေါ်ရှိ မြင့်မားသောကြိမ်နှုန်း RF နှင့် 5G စက်ပစ္စည်းများ

semi-insulating SiC wafer platform များပေါ်တွင် တည်ဆောက်ထားသော RF amplifier များနှင့် switch များသည် သာလွန်ကောင်းမွန်သော thermal conductivity နှင့် breakdown voltage ကို ပြသသည်။ SiC wafer substrate သည် GHz ကြိမ်နှုန်းများတွင် dielectric losses များကို လျှော့ချပေးပြီး SiC wafer ၏ ပစ္စည်းခိုင်ခံ့မှုသည် မြင့်မားသော power နှင့် မြင့်မားသော အပူချိန်အခြေအနေများတွင် တည်ငြိမ်စွာလည်ပတ်နိုင်စေသည်—SiC wafer ကို နောက်မျိုးဆက် 5G base station များနှင့် radar system များအတွက် ရွေးချယ်မှု substrate ဖြစ်စေသည်။ -

SiC Wafer မှ Optoelectronic နှင့် LED Substrates များ

SiC wafer အောက်ခံများပေါ်တွင် စိုက်ပျိုးထားသော အပြာရောင်နှင့် UV LED များသည် အလွန်ကောင်းမွန်သော lattice matching နှင့် အပူပျံ့နှံ့မှုမှ အကျိုးကျေးဇူးရရှိပါသည်။ ඔප දැමීමရှိသော C-face SiC wafer ကိုအသုံးပြုခြင်းသည် epitaxial အလွှာများကို တစ်ပြေးညီဖြစ်စေပြီး SiC wafer ၏ မွေးရာပါမာကျောမှုသည် wafer ကို ပါးလွှာစေပြီး ယုံကြည်စိတ်ချရသော device packaging ကို ဖြစ်စေပါသည်။ ၎င်းသည် SiC wafer ကို မြင့်မားသောပါဝါ၊ ကြာရှည်ခံ LED အသုံးချမှုများအတွက် go-to platform ဖြစ်စေသည်။

SiC ဝေဖာ၏ မေးခွန်းများနှင့် အဖြေများ

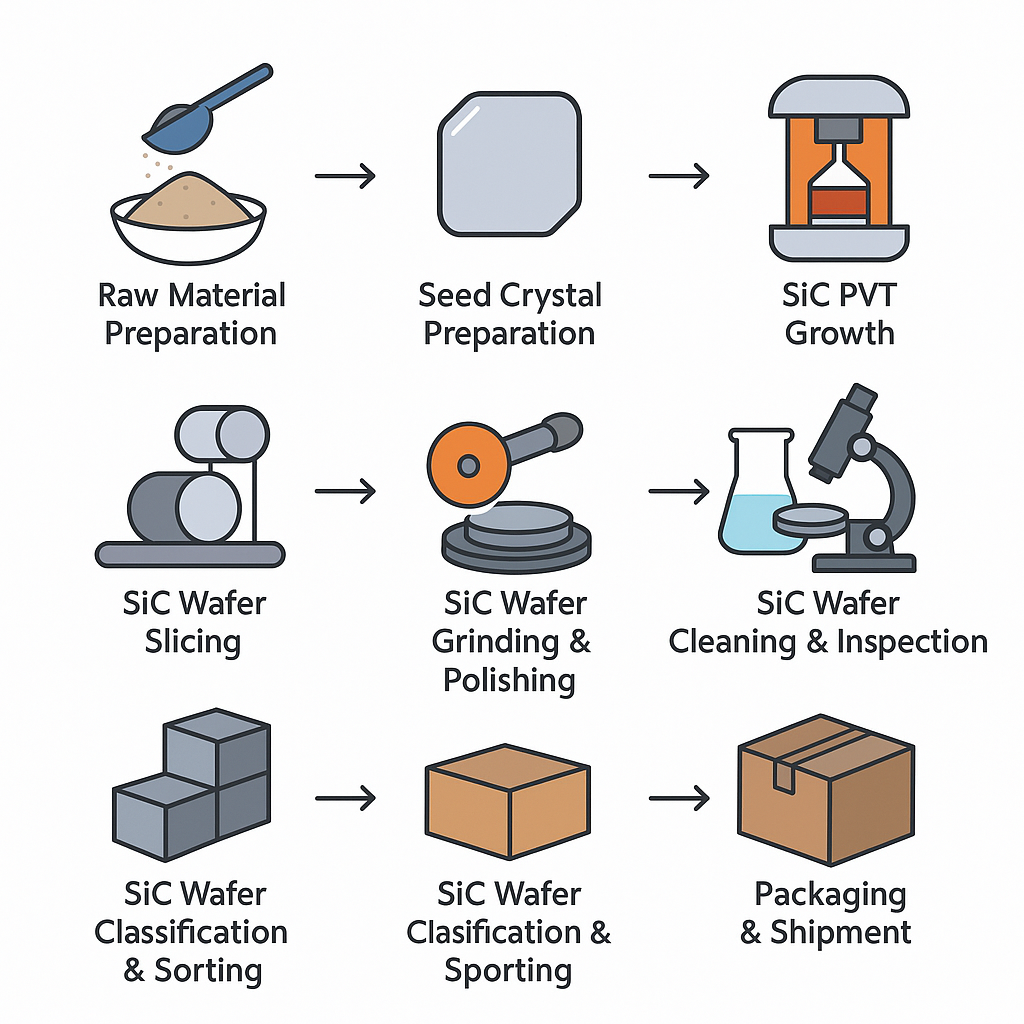

၁။ မေး- SiC ဝေဖာများကို မည်သို့ထုတ်လုပ်သနည်း။

က:

ထုတ်လုပ်ထားသော SiC ဝေဖာများအသေးစိတ်အဆင့်များ

-

SiC ဝေဖာများကုန်ကြမ်းပစ္စည်းပြင်ဆင်ခြင်း

- ≥5N-အဆင့် SiC အမှုန့် (အညစ်အကြေး ≤1 ppm) ကိုသုံးပါ။

- ကျန်ရှိနေသော ကာဗွန် သို့မဟုတ် နိုက်ထရိုဂျင် ဒြပ်ပေါင်းများကို ဖယ်ရှားရန် ဇကာဖြင့် စစ်ပြီး ကြိုတင်ဖုတ်ပါ။

-

SiCမျိုးစေ့ပုံဆောင်ခဲပြင်ဆင်ခြင်း

-

4H-SiC တစ်ခုတည်းသော ပုံဆောင်ခဲ အပိုင်းအစတစ်ခုကိုယူ၍ 〈0001〉 ဦးတည်ချက်အတိုင်း ~10 × 10 mm² အထိ လှီးဖြတ်ပါ။

-

Ra ≤0.1 nm အထိ တိကျစွာ ඔප දැමීමပြီး ပုံဆောင်ခဲ ဦးတည်ချက်ကို မှတ်သားပါ။

-

-

SiCPVT ကြီးထွားမှု (ရုပ်ပိုင်းဆိုင်ရာ အငွေ့သယ်ယူပို့ဆောင်ရေး)

-

ဂရပ်ဖိုက် ခွက်ကို ထည့်ပါ။ အောက်ခြေတွင် SiC အမှုန့်ထည့်ပြီး အပေါ်မှ အစေ့ပုံဆောင်ခဲ ထည့်ပါ။

-

Torr 10⁻³–10⁻⁵ အထိ စွန့်ထုတ်ပါ သို့မဟုတ် 1 atm တွင် မြင့်မားသောသန့်စင်မှု ဟီလီယမ်ဖြင့် ပြန်လည်ဖြည့်ပါ။

-

အပူရင်းမြစ်ဇုန်ကို ၂၁၀၀–၂၃၀၀ ဒီဂရီစင်တီဂရိတ်တွင်ထားပါ၊ မျိုးစေ့ဇုန်ကို ၁၀၀–၁၅၀ ဒီဂရီစင်တီဂရိတ်ထက် ပိုအေးအောင်ထားပါ။

-

အရည်အသွေးနှင့် ထုတ်လုပ်မှုပမာဏကို ဟန်ချက်ညီစေရန်အတွက် ကြီးထွားမှုနှုန်းကို ၁–၅ မီလီမီတာ/နာရီတွင် ထိန်းချုပ်ပါ။

-

-

SiCခဲတုံးများကို အပူပေးခြင်း

-

ကြီးထွားပြီးသား SiC အချောင်းကို ၁၆၀၀ မှ ၁၈၀၀ ဒီဂရီစင်တီဂရိတ်တွင် ၄ နာရီမှ ၈ နာရီအထိ အပူပေးပါ။

-

ရည်ရွယ်ချက်: အပူဖိစီးမှုများကို သက်သာစေပြီး နေရာရွေ့သိပ်သည်းဆကို လျှော့ချပေးသည်။

-

-

SiCဝေဖာလှီးဖြတ်ခြင်း

-

စိန်ဝါယာလွှကို အသုံးပြု၍ အချောင်းကို ၀.၅–၁ မီလီမီတာ အထူရှိသော ဝေဖာများအဖြစ် လှီးဖြတ်ပါ။

-

အက်ကွဲကြောင်းငယ်များ မဖြစ်ပေါ်စေရန် တုန်ခါမှုနှင့် ဘေးတိုက်အားကို အနည်းဆုံးဖြစ်အောင် ပြုလုပ်ပါ။

-

-

SiCဝေဖာကြိတ်ခွဲခြင်းနှင့် ඔප දැමීම

-

ကြမ်းတမ်းစွာကြိတ်ခြင်းလွှစက်ပျက်စီးမှုကို ဖယ်ရှားရန် (ကြမ်းတမ်းမှု ~10–30 µm)။

-

အနုစိတ်ကြိတ်ခွဲခြင်းပြားချပ်မှု ≤5 µm ရရှိရန်။

-

ဓာတု-စက်ပိုင်းဆိုင်ရာ ඔප දැමීම (CMP)မှန်ကဲ့သို့ အပြီးသတ်ခြင်း (Ra ≤0.2 nm) သို့ ရောက်ရှိရန်။

-

-

SiCဝေဖာသန့်ရှင်းရေးနှင့် စစ်ဆေးခြင်း

-

အသံလှိုင်းဖြင့် သန့်ရှင်းရေးလုပ်ခြင်းPiranha ဖြေရှင်းချက် (H₂SO₄:H₂O₂)၊ DI ရေ၊ ထို့နောက် IPA တွင်။

-

XRD/ရာမန်ရောင်စဉ်တန်း စစ်ဆေးခြင်းpolytype (4H၊ 6H၊ 3C) ကို အတည်ပြုရန်။

-

အပြန်အလှန် တိုင်းတာခြင်းပြားချပ်မှု (<5 µm) နှင့် လိမ်ကောက်မှု (<20 µm) ကို တိုင်းတာရန်။

-

လေးချက်စမ်းသပ်ကိရိယာခုခံအားကို စမ်းသပ်ရန် (ဥပမာ HPSI ≥10⁹ Ω·cm)။

-

ချို့ယွင်းချက်စစ်ဆေးခြင်းpolarized light မိုက်ခရိုစကုပ်နှင့် scratch tester အောက်တွင်။

-

-

SiCဝေဖာအမျိုးအစားခွဲခြားခြင်းနှင့် စီခြင်း

-

ဝေဖာများကို polytype နှင့် electrical type အလိုက် စီပါ-

-

4H-SiC N-အမျိုးအစား (4H-N): သယ်ဆောင်သူပါဝင်မှု 10¹⁶–10¹⁸ cm⁻³

-

4H-SiC မြင့်မားသောသန့်စင်မှု တစ်ဝက်လျှပ်ကာ (4H-HPSI): ခုခံမှု ≥10⁹ Ω·cm

-

6H-SiC N-အမျိုးအစား (6H-N)

-

အခြားသူများ: 3C-SiC၊ P-အမျိုးအစား၊ စသည်တို့။

-

-

-

SiCဝေဖာထုပ်ပိုးခြင်းနှင့် ပို့ဆောင်ခြင်း

၂။ မေး- ဆီလီကွန်ဝေဖာများထက် SiC ဝေဖာများ၏ အဓိကအားသာချက်များကား အဘယ်နည်း။

A: ဆီလီကွန်ဝေဖာများနှင့် နှိုင်းယှဉ်ပါက SiC ဝေဖာများသည် အောက်ပါတို့ကို လုပ်ဆောင်နိုင်သည်-

-

ဗို့အားမြင့် လည်ပတ်မှု(>1,200 V) ဖြင့် on-resistance နိမ့်သည်။

-

အပူချိန်တည်ငြိမ်မှုမြင့်မားခြင်း(၃၀၀ ဒီဂရီစင်တီဂရိတ်ထက် ပိုမြင့်သည်) နှင့် အပူချိန်စီမံခန့်ခွဲမှုကို ပိုမိုကောင်းမွန်စေသည်။

-

ပိုမိုမြန်ဆန်သော ကူးပြောင်းမှုမြန်နှုန်းများswitching losses နည်းပါးခြင်း၊ system-level cooling နှင့် power converters များ၏ အရွယ်အစားကို လျှော့ချပေးခြင်း။

၄။ မေး- SiC wafer အထွက်နှုန်းနှင့် စွမ်းဆောင်ရည်ကို မည်သည့်ချို့ယွင်းချက်များက သက်ရောက်မှုရှိသနည်း။

A: SiC ဝေဖာများတွင် အဓိကချို့ယွင်းချက်များတွင် မိုက်ခရိုပိုက်များ၊ အခြေခံပြားအဆစ်လွဲခြင်း (BPDs) နှင့် မျက်နှာပြင်ခြစ်ရာများ ပါဝင်သည်။ မိုက်ခရိုပိုက်များသည် စက်ပစ္စည်းချို့ယွင်းမှုကို ဆိုးရွားစွာဖြစ်စေနိုင်သည်။ BPD များသည် အချိန်ကြာလာသည်နှင့်အမျှ on-resistance တိုးလာပြီး မျက်နှာပြင်ခြစ်ရာများသည် ဝေဖာကျိုးခြင်း သို့မဟုတ် epitaxial ကြီးထွားမှုညံ့ဖျင်းခြင်းကို ဖြစ်စေသည်။ ထို့ကြောင့် SiC ဝေဖာအထွက်နှုန်းကို အမြင့်ဆုံးဖြစ်စေရန်အတွက် တင်းကျပ်သောစစ်ဆေးမှုနှင့် ချို့ယွင်းချက်လျှော့ချရေးသည် မရှိမဖြစ်လိုအပ်သည်။

ပို့စ်တင်ချိန်: ၂၀၂၅ ခုနှစ်၊ ဇွန်လ ၃၀ ရက်